ASAI-PT

Issue 1 June 2005 503

Receive FIFO Error Counter Test (#625)

This test reads and clears the BRI port’s Receive FIFO error counter maintained on the TN800

circuit pack. This counter is incremented by the circuit pack when it detects an overflow of its

receive buffers. The test passes if the value of the counter is 0 (that is, the error is cleared). If

the counter is not zero, the test fails, and the value of the counter is displayed in the Error Code

field.

This error can occur if signaling frames are being received from a packet bus at a rate sufficient

to overflow the receive buffers on the circuit pack for a port or if hardware fault is causing the

receive buffers not to be emptied properly. This test is useful for verifying the repair of the

problem.

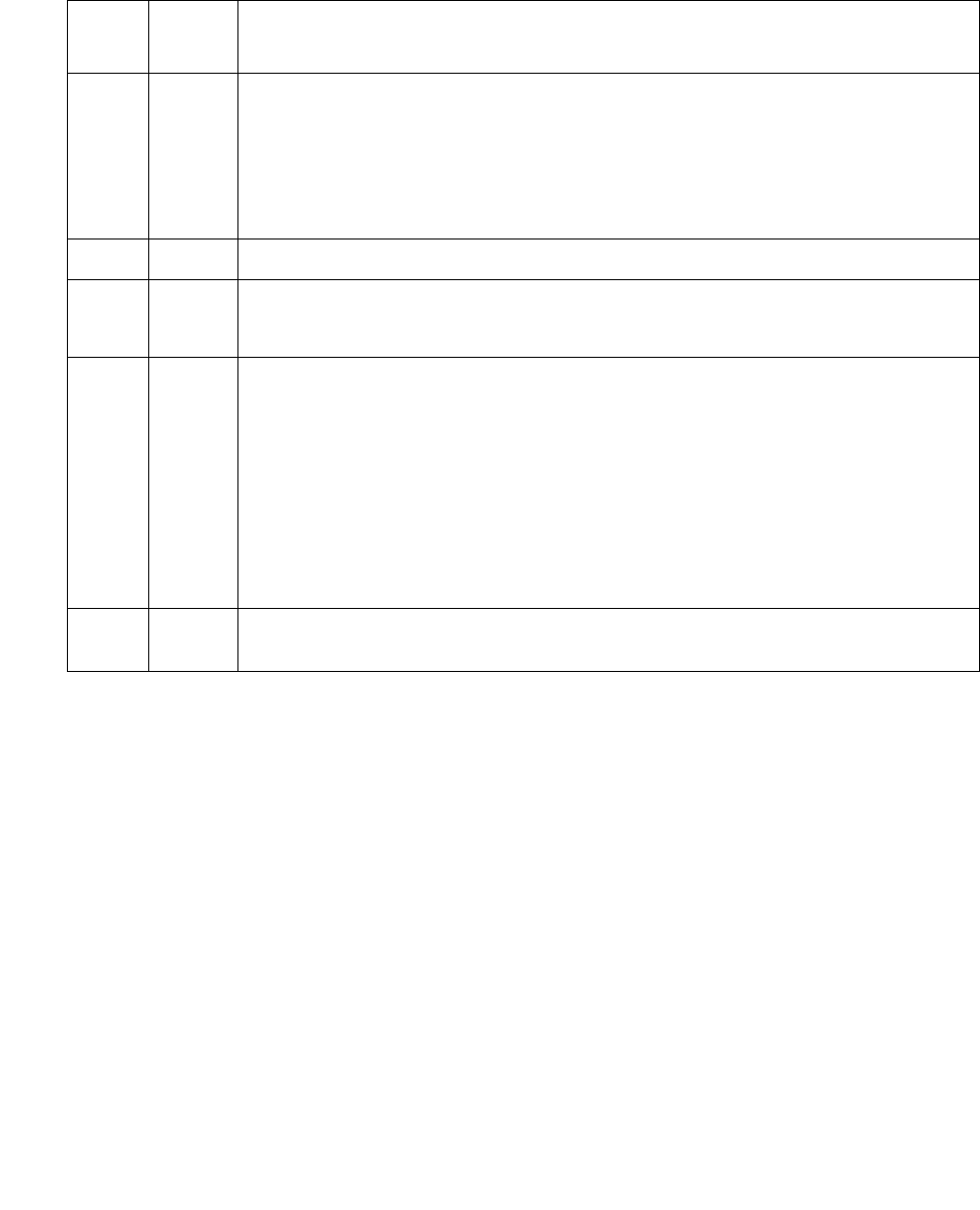

Table 154: Test #624 Layer 1 Transmission Error Counter Test

Error

Code

Test

Result

Description / Recommendation

2000 ABRT Response was not received from the circuit pack within the allowable time

period.

1. If the test aborts repeatedly up to 5 times, reset the circuit pack using

busyout board location and reset board location.

2. If the test aborts again, replace the circuit pack.

2012 ABRT Internal system error

2100 ABRT Could not allocate necessary system resources to run test.

1. Retry the command at 1-minute intervals up to 5 times.

Any FAIL The TN800 circuit pack is still detecting errors of this type. The Error Code

field contains the value of this counter.

1. Retry the command at 1-minute intervals up to 5 times.

2. If the test continues to fail, review the results of other tests in the long

test sequence. Note the results of the Level 1 Status Inquiry test.

Follow the repair procedures for any of the executed tests if they fail.

Otherwise, go to the next step.

3. Replace the circuit pack.

PASS The Layer 1 Transmission error counter was read correctly and has a value

of 0.