DS1-FAC (DS1 Facility)

Issue 1 June 2005 1069

System Technician-Demanded Tests:

Descriptions And Error Codes

Investigate tests in the order presented. By clearing error codes associated with the Failure

Audit, you may clear errors generated from other tests in the sequence. Use test board to

run Failure Audit.

.

Far-End Internal Loop-Back Test (#797)

This test is destructive.

This test starts at the DS1 converter circuit pack whose equipment location was entered and

traverses over the specified facility and loops at the internal facility interface on the other DS1

converter circuit pack in the DS1 converter complex. See the following diagram.

Every part of this test is executed under firmware control and the result is sent back to the

maintenance software. The test is executed by sending digital data through every DS1 channel

on this facility. For TN574 DS1 Converter facilities, test patterns are sent through every DS1

channel. For TN1654 DS1 Converter facilities, test patterns are sent through one DS1 channel.

If there is only one DS1 facility available, the system will not allow that last facility to be busied

out. In that case, the DS1 converter circuit pack must be busied out before executing this test.

For a standard-, duplex-, or high-reliability system (no PNC duplication), if there is only one DS1

facility available, then this test can only be executed at the endpoint that is closer to the media

server relative to the neighbor DS1 converter circuit pack because of its impacts on the system

control links. For TN574 DS1 converter boards, the completion of the test will be delayed in this

configuration to wait for the recovery of the system control links. For a critical-reliability system

(PNC duplication) or for a system with multiple DS1 facilities, the test can be executed at any

DS1 converter circuit pack.

If the test passes on a TN1654 DS1 facility, the round trip delay time appears in milliseconds in

the Error Code field. The round trip delay time is the length of time in milliseconds it takes for

the firmware to receive the test pattern after it has been sent.

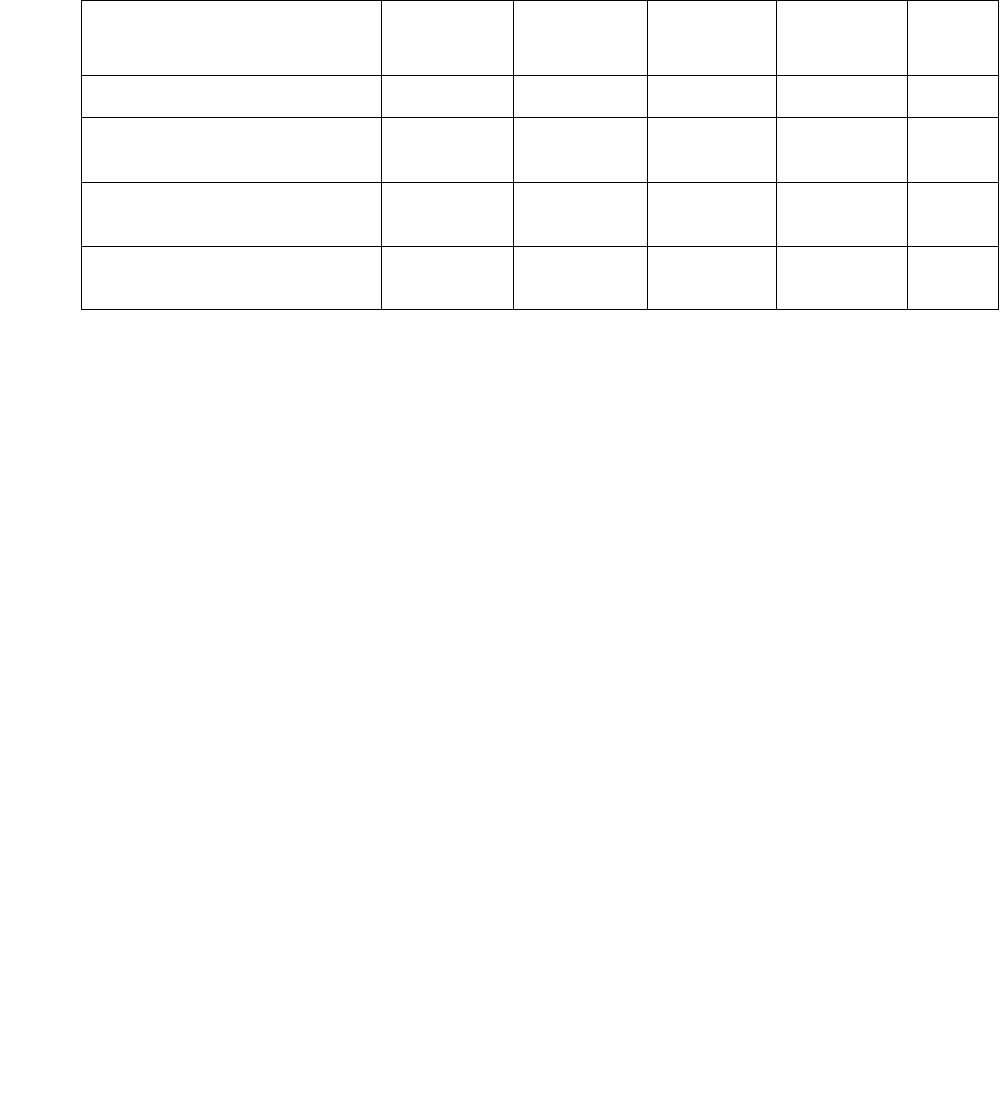

Order of Investigation Short Test

Sequence

Long Test

Sequence

External

Loopback

Reset

Sequence

D/ND

1

1. D = Destructive; ND = Nondestructive

Failure Audit (#949) ND

DS1 Interface Options Audit

(#798)

XX ND

Far-End Internal Loopback

(#797)

XD

Near-End External

Loopback test (#799)

XD