UDS1-BD (UDS1 Interface Circuit Pack)

Issue 1 June 2005 2457

1039 ABRT The UDS1 Interface circuit pack is providing timing for the system.

Executing this test could cause major system disruption.

If the UDS1 Interface circuit pack needs to be tested, set the

synchronization reference to another DS1 Interface circuit pack or to the

IPSI or Tone-Clock circuit pack via the following command sequence:

1. Enter disable synchronization-switch.

2. Enter set synchronization location.

3. Enter enable synchronization-switch.

Rerun the test. If the test aborts again, a different ABRT code will be

generated. Follow the recommended maintenance procedures for the Error

Code.

1950 ABRT Another loopback/span test is already executing on the DS1 board or the

board is in a network-requested loop-back mode (line loopback or payload

loopback). The hardware error log will indicate whether a Customer

Loop-Back Jack test, Far CSU Loopback test, or the One-Way Span test is

executing or if the board is in line-loopback or payload-loop-back mode.

Only one long-duration loopback/span test can be active at a given time. If a

loopback/span test is already active, terminate the test with test

ds1-loop location end-loopback/span-test in order to execute

this test.

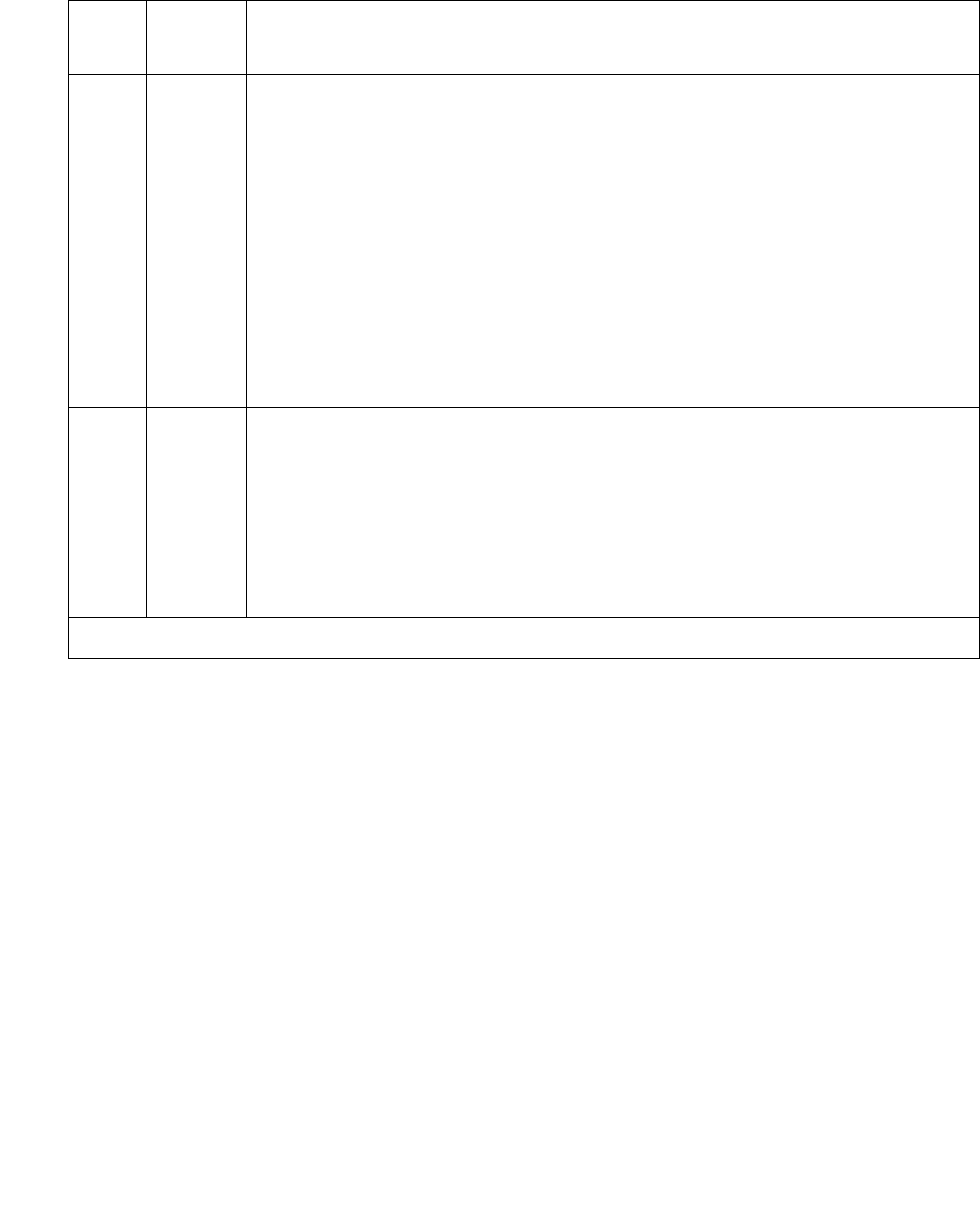

Table 870: Test #1212 CPE Loop-Back Jack Test (continued)

Error

Code

Test

Result

Description / Recommendation

2 of 4