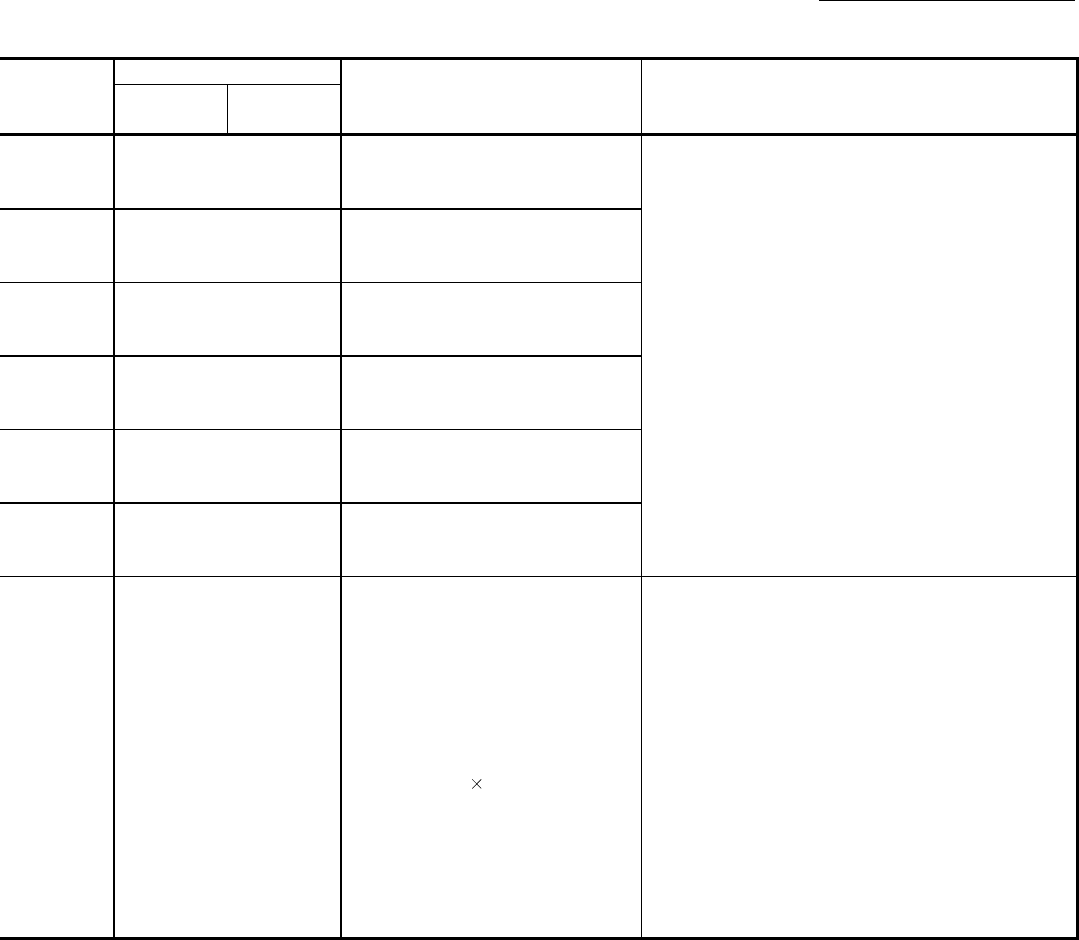

16 - 43

Chapter 16 Troubleshooting

Related buffer memory address

Set range

(Setting with sequence program)

Remedy

QD77MS2

QD77MS4

QD77MS16

36+150n

37+150n

1 to 8388608

With the setting brought into the setting range, turn the PLC

READY signal [Y0] from OFF to ON.

38+150n

39+150n

1 to 8388608

40+150n

41+150n

1 to 8388608

42+150n

43+150n

1 to 8388608

44+150n

45+150n

1 to 8388608

46+150n

47+150n

1 to 8388608

48+150n

49+150n

<JOG speed limit value>

1 to 1000000000 [PLS/s]

1 to 2000000000 [

10

-2

mm/min or others]

• With the setting brought into the setting range, turn the PLC

READY signal [Y0] from OFF to ON.

• Bring the setting into the speed limit value or below.

n: Axis No.-1