7 - 86

7 OPERATION CONTROL PROGRAMS

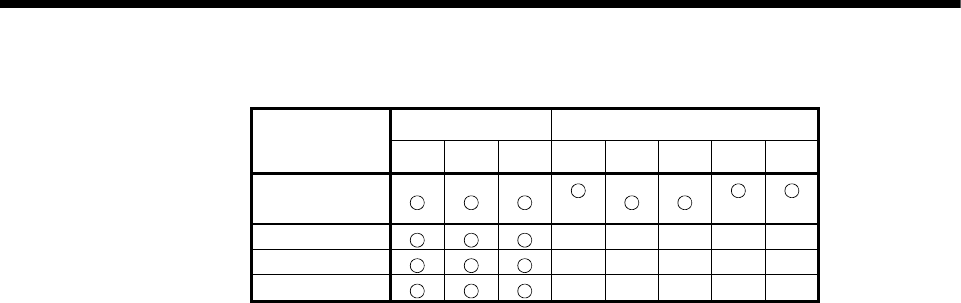

(2) The word devices that may be set at (D), (S), (n) and (D1) are shown below.

Word devices

(Note-1)

Bit devices

(Note-1), (Note-2)

Setting data

Dn Wn #n Mn Bn Fn Xn Yn

(D)

(Note-3)

(Note-4)

(Note-4)

(S)

— — — — —

(n)

— — — — —

(D1)

— — — — —

(Note-1) : The device No. cannot be specified indirectly.

(Note-2) : Specify a multiple of 16 as the device number of bit data.

(Note-3) : Special relays (M9000 to M9255) and dedicated devices (M2000 to M2399) cannot be set.

(Note-4) : PX/PY cannot be set.

(3) When data are read normally from the target CPU specified with (S1), the reading

complete flag M9216 to M9219 (CPU No.1 : M9216, CPU No.2 : M9217, CPU

No.3 : M9218, CPU No.4 : M9219) corresponding to the target CPU turns on. If

data cannot be read normally, the reading complete flag of the target CPU does

not turn on.

(4) Adjust an executive task, the number of transfer word referring to the operation

processing time so that this instruction may not obstruct the execution of the

motion operation because processing time becomes long in argument to the

number of words (n) to be written.

(5) When multiple MULTR instructions are executed to the same CPU

simultaneously, the reading complete flag M9216 to M9219 turns on/as a result of

MULTR that it is executed at the end.

(6) Reset the reading complete flag (M9126 to M9219) using the user program.

[Errors]

(1) An operation error will occur if:

• Number of words (n) to be read is outside the range of 1 to 256.

• The shared CPU memory first address (S2) of the data which it will be read is

outside the range (000H to FFFH) of the shared CPU memory address.

• The shared CPU memory first address (S2) of the data which it will be read +

number of words (n) to be read is outside the range (000H to FFFH) of the

shared CPU memory address.

• First device No. (D) which stores the reading data + number of words (n) to be

read is outside the device range.

• Except 3E0H/3E1H/3E2H/3E3H is set at (S1).

• The self CPU is specified with (S1).

• The CPU which reads is resetting.

• The errors are detected in the CPU which read.

• (D) is a bit device and device number is not a multiple of 16.

• PX/PY is set in (D) to (D)+(n-1).