135

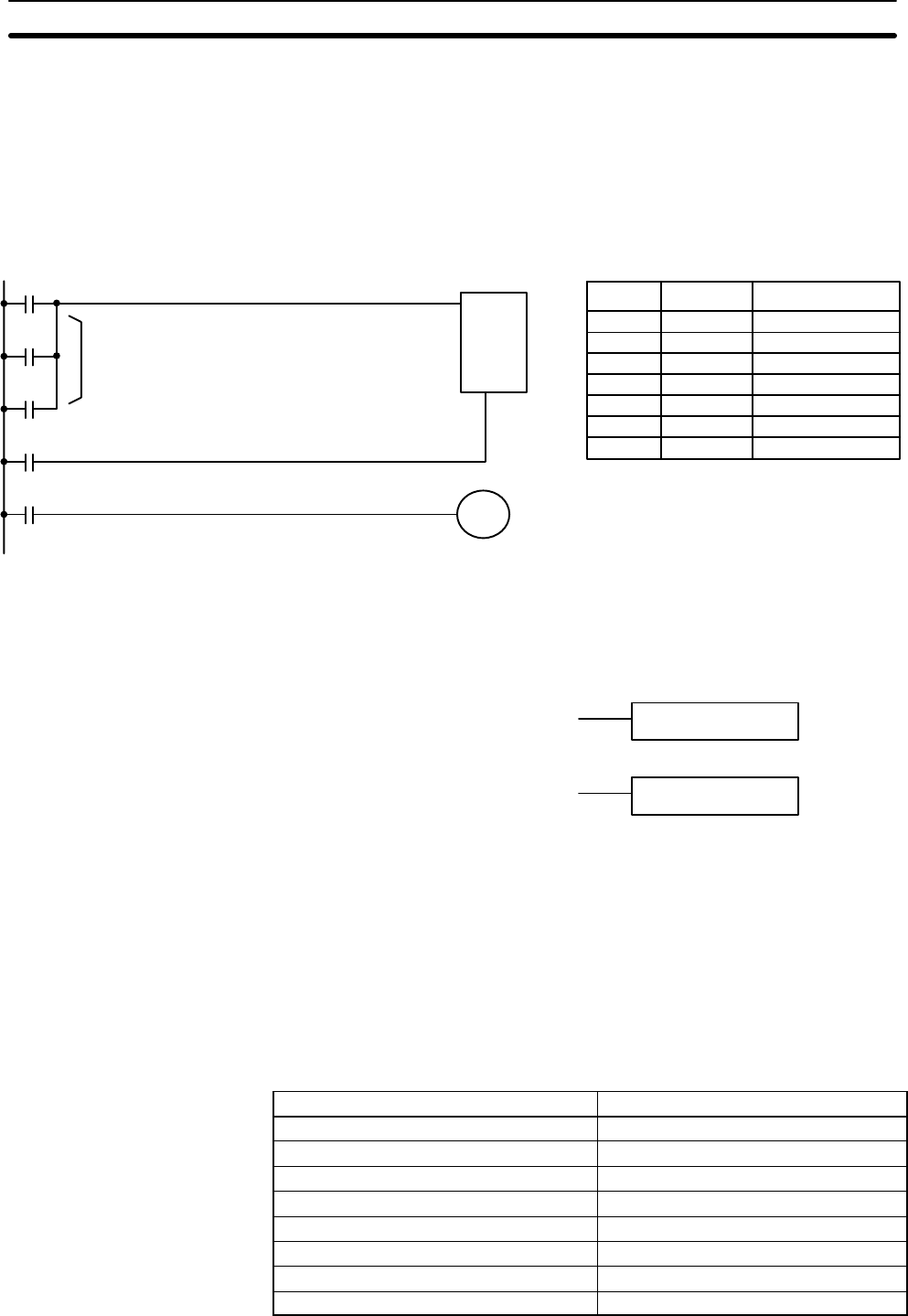

Example If a HR bit or an AR bit is used, bit status will be retained even during a power

interruption. KEEP(11) can thus be used to program bits that will maintain status

after restarting the PC following a power interruption. An example of this that can

be used to produce a warning display following a system shutdown for an emer-

gency situation is shown below. Bits 00002, 00003, and 00004 would be turned

ON to indicate some type of error. Bit 00005 would be turned ON to reset the

warning display. HR 0000, which is turned ON when any one of the three bits

indicates an emergency situation, is used to turn ON the warning indicator

through 00500.

HR 0000

00500

00002

00003

00004

00005

Reset input

Indicates

emergency

situation

Activates

warning

display

S

R

KEEP(11)

B

Address Instruction Operands

00000 LD 00002

00001 OR 00003

00002 OR 00004

00003 LD 00005

00004 KEEP(11) HR 0000

00005 LD HR 0000

00006 OUT 00500

KEEP(11) can also be combined with TIM to produce delays in turning bits ON

and OFF. Refer to

5-14-1 TIMER – TIM

for details.

5-10 INTERLOCK and INTERLOCK CLEAR – IL(02) and ILC(03)

Ladder Symbol

IL(02)

Ladder Symbol

ILC(03)

Description IL(02) is always used in conjunction with ILC(03) to create interlocks. Interlocks

are used to enable branching in the same way as can be achieved with TR bits,

but treatment of instructions between IL(02) and ILC(03) differs from that with

TR bits when the execution condition for IL(02) is OFF. If the execution condition

of IL(02) is ON, the program will be executed as written, with an ON execution

condition used to start each instruction line from the point where IL(02) is located

through the next ILC(03). Refer to

4-7-7 Branching Instruction Lines

for basic

descriptions of both methods.

If the execution condition for IL(02) is OFF, the interlocked section between

IL(02) and ILC(03) will be treated as shown in the following table:

Instruction Treatment

OUT and OUT NOT Designated bit turned OFF.

SET and RSET Bit status maintained.

TIM and TIMH(15) Reset.

TTIM(87) PV maintained.

CNT, CNTR(12) PV maintained.

KEEP(11) Bit status maintained.

DIFU(13) and DIFD(14) Not executed (see below).

All others Not executed.

INTERLOCK and INTERLOCK CLEAR – IL(02) and ILC(03) Section 5-10