Chapter 6 Advanced Topics 55

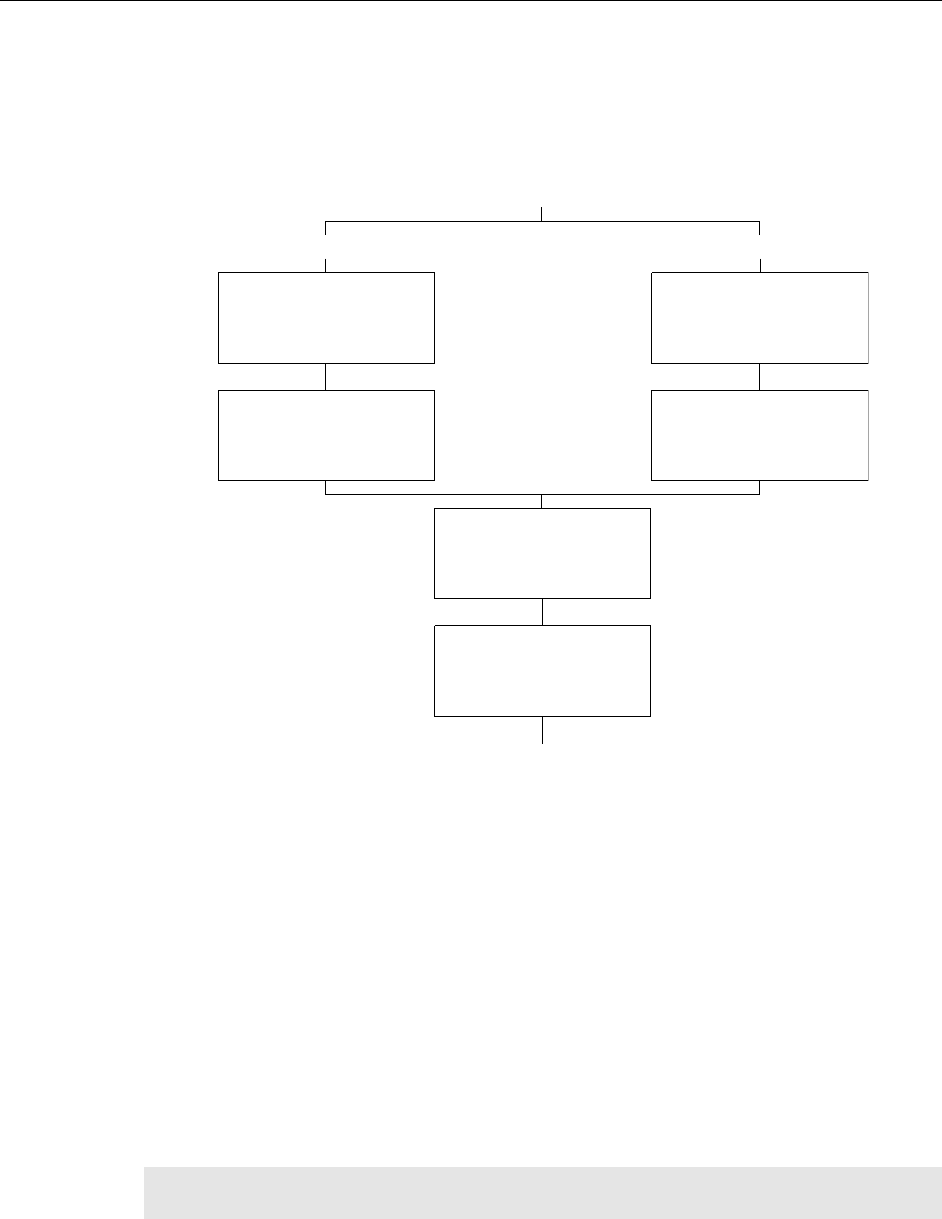

External Sync with Continuous Cleans

Another timing mode available with the ST-133 controller is called Continuous Cleans.

In addition to the standard "cleaning" of the array, which occurs after the controller is

enabled, Continuous Cleans will remove any charge that integrates on the array between

the time that the Start Acquisition command is received by the controller and the moment

that the External Sync pulse trigger edge is received.

Shutter opens

Shutter remains open

for preprogrammed

exposure time

System waits while

shutter closes

Shutter opens

CCD is continuously

cleaned until External Sync

pulse is received

(shutter preopen) (shutter normal)

CCD is continuously

cleaned until External Sync

pulse is received

Figure 19. Continuous Cleans Operation Flowchart

Once the External Sync pulse trigger edge is received, cleaning of the array stops as soon

as the current row is shifted, and frame collection begins: a delay time of up to one row

shift can be expected. With Normal Shutter operation the shutter is opened for the set

exposure time. With PreOpen Shutter operation the shutter is open during the continuous

cleaning, and once the External Sync pulse trigger edge is received the shutter remains

open for the set exposure time, then closes. If the vertical rows are shifted midway when

the External Sync pulse trigger edge arrives, the pulse is saved until the row shifting is

completed, to prevent the CCD from getting “out of step.” As expected, the response

latency is on the order of one vertical shift time, from 1-30 sec depending on the array.

This latency does not prevent the incoming signal from being detected, since photo

generated electrons are still collected over the entire active area. However, if the signal

arrival is coincident with the vertical shifting, image smearing of up to one pixel is

possible. The amount of smearing is a function of the signal duration compared to the

single vertical shift time.

Note: If EXT SYNC is still active (in Figure 20, this means that if it is still LOW) at the

end of the readout, the hardware may interpret this as a second sync pulse, and so on.