2 - 19

2 MULTIPLE CPU SYSTEM

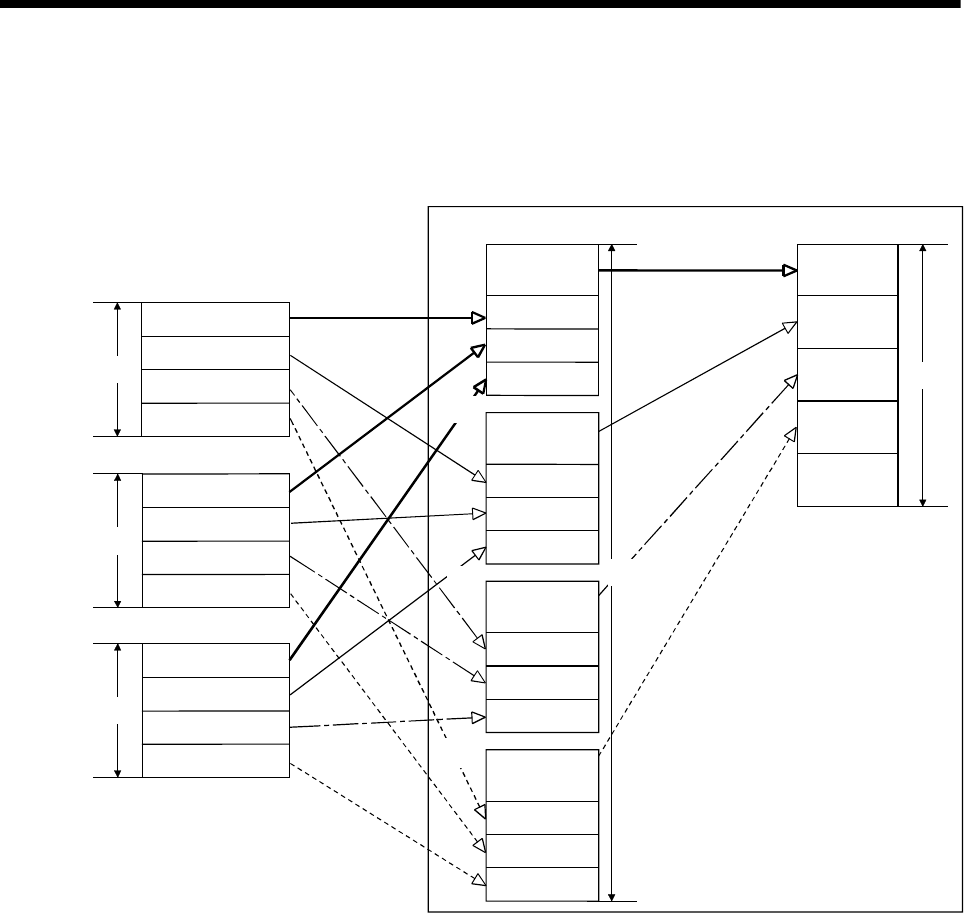

3) The block diagram below illustrates the automatic refresh operation over

four ranges of setting 1: link relay (B), setting 2: link register (W), setting

3: data register (D), and setting 4: internal relay (M).

CPU No.2

transmitting data (No.3)

CPU No.2

transmitting data (No.2)

CPU No.2

transmitting data (No.4)

CPU No.2

receiving data (No.1)

CPU No.3

receiving data (No.1)

CPU No.4

receiving data (No.1)

CPU No.1

transmitting data

(No.1)

to

M0

Device

CPU No.2

Maximum

2k words

Shared CPU memory

of other CPU

User-defined area

Shared CPU memory

Maximum

2k words

CPU No.1

Read via END processing

of CPU No.1

Write during END processing

W

r

i

t

e

d

u

r

i

n

g

E

N

D

p

r

o

c

e

s

s

i

n

g

W

r

i

t

e

d

u

r

i

n

g

E

N

D

p

r

o

c

e

s

s

i

n

g

W

r

i

t

e

d

u

r

i

n

g

E

N

D

p

r

o

c

e

s

s

i

n

g

Maximum

8k words

CPU No.2

receiving data (No.2)

CPU No.3

receiving data (No.2)

CPU No.4

receiving data (No.2)

CPU No.1

transmitting data

(No.2)

CPU No.2

receiving data (No.3)

CPU No.3

receiving data (No.3)

CPU No.4

receiving data (No.3)

CPU No.1

transmitting data

(No.3)

CPU No.2

receiving data (No.4)

CPU No.3

receiving data (No.4)

CPU No.4

receiving data (No.4)

CPU No.1

transmitting data

(No.4)

CPU No.2

transmitting data (No.1)

CPU No.1

transmitting data

(No.1)

CPU No.1

transmitting data

(No.2)

CPU No.1

transmitting data

(No.3)

CPU No.1

transmitting data

(No.4)

Setting 2

W0

Setting 1

B0

Setting 3

D0

Setting 4

M0

CPU No.3

transmitting data (No.3)

CPU No.3

transmitting data (No.2)

CPU No.3

transmitting data (No.4)

CPU No.3

Maximum

2k words

CPU No.3

transmitting data (No.1)

CPU No.4

transmitting data (No.3)

CPU No.4

transmitting data (No.2)

CPU No.4

transmitting data (No.4)

CPU No.4

Maximum

2k words

CPU No.4

transmitting data (No.1)