596

FX3S/FX3G/FX3GC/FX3U/FX3UC Series

Programming Manual - Basic & Applied Instruction Edition

24 Others – FNC181 to FNC189

24.5 FNC189 – HCMOV / High-Speed Counter Move

24.5 FNC189 – HCMOV / High-Speed Counter Move

Outline

This instruction updates the current value of a specified high-speed counter or ring counter.

The function of this instruction varies depending on the PLC version.

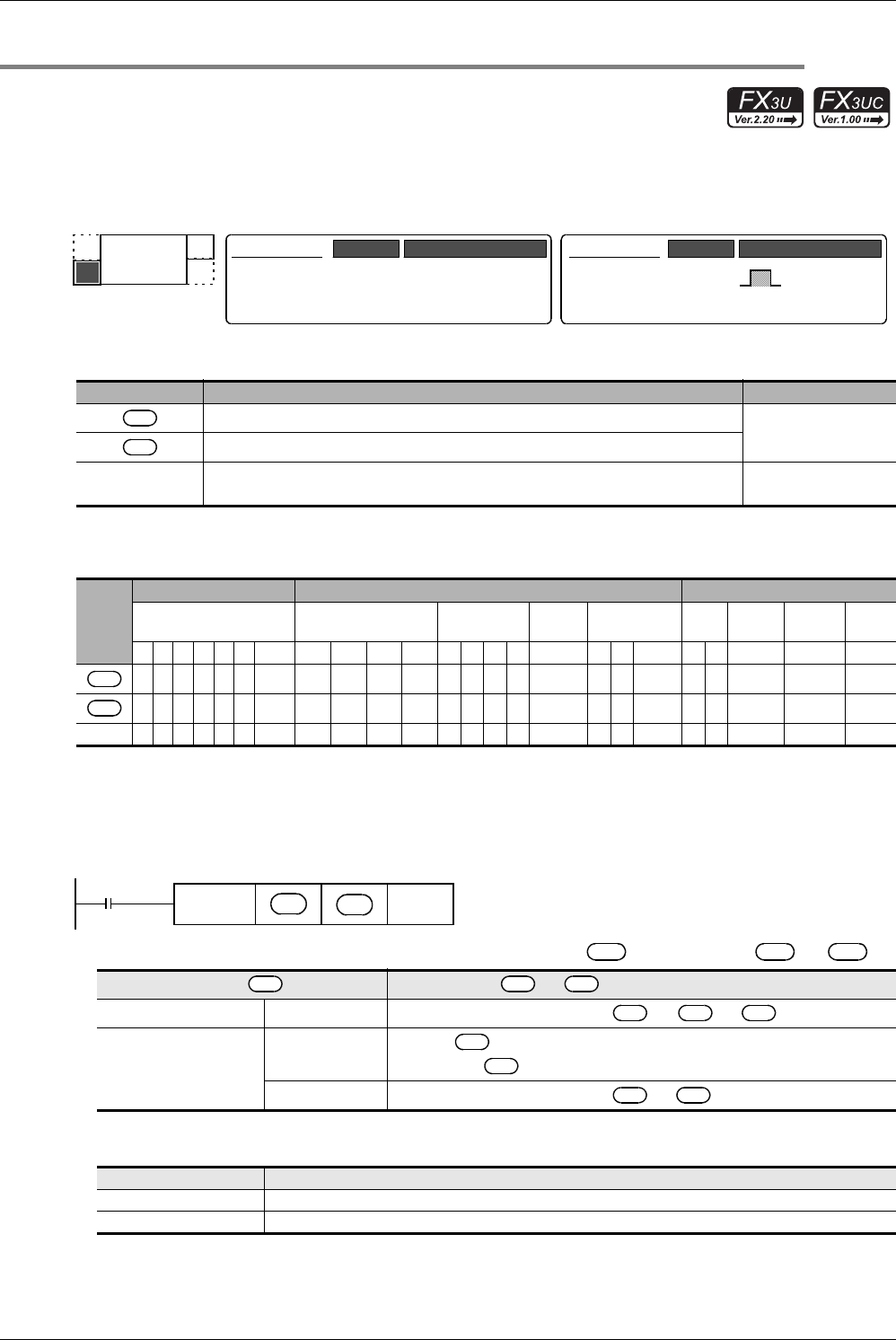

1. Instruction format

2. Set data

*1. Ring counters (D8099 and D8398) cannot be specified in FX3UC PLCs before Ver. 2.20.

3. Applicable devices

S: Only high-speed counters (C235 to C255) and ring counters (D8099 and D8398) can be specified.

Explanation of function and operation

1. 32-bit operation (DHCMOV)

• The current value of a high-speed counter or ring counter specified in is transferred to [ +1, ].

• After transfer, the current value of the high-speed counter or ring counter is processed as shown in the table below

depending on the set value of "n":

Operand Type Description Data Type

Device number of high-speed counter or ring counter*

1

handled as transfer source

32-bit binary

Device number handled as transfer destination

n

Specification to clear the current value of high-speed counter or ring counter

*1

(transfer

source) after transfer [clear (K1), no clear (K0)]

16-bit binary

Oper-

and

Type

Bit Devices Word Devices Others

System User Digit Specification System User

Special

Unit

Index

Con-

stant

Real

Number

Charac-

ter String

Pointer

XYMTCSD

.b KnX KnY KnM KnS T C D R

U\G

V Z Modify K H E "

"P

SS

n

Device [ +1, ] after instruction is executed

High-speed counter C235 to C255

Current value of high-speed counter → [+1, ]

Ring counter

D8099

D8099 →

"0" is stored in +1.

D8398

Current value of [D8399, D8398] → [+1, ]

"n" set value Operation

K0 (H0) Does not clear the current value (no processing).

K1 (H1) Clears the current value to "0".

D

FNC 189

HCMOV

Mnemonic Operation Condition

16-bit Instruction

13 steps

DHCMOV

Mnemonic Operation Condition

Continuous

Operation

32-bit Instruction

⎯

⎯

⎯

S

D

S

D

FNC189

DHCMOV

n

S

D

Command

input

S D D

S D D

S D D

D

D

D D