Configuration

3-39

9124-A2-LB20-00

March 2000

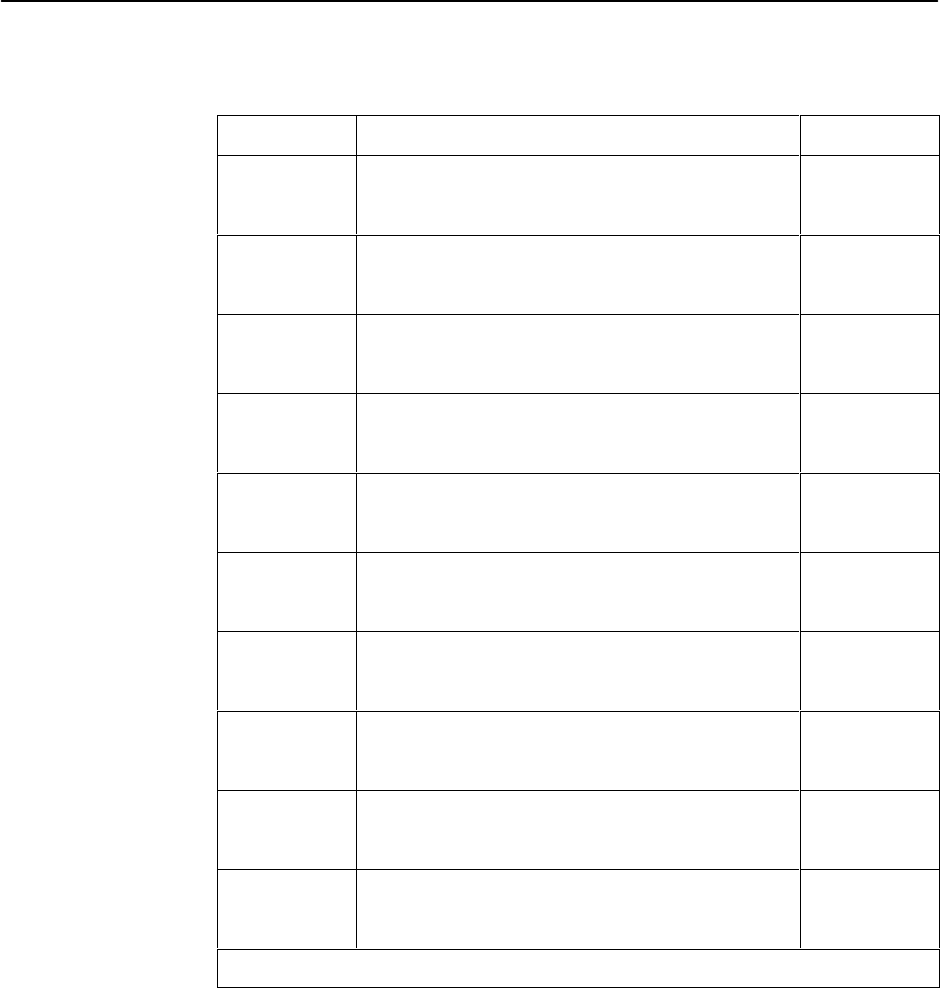

Table 3-7. Signaling and Trunk Conditioning Values (3 of 3)

Network Side DSX-1 SideMeaning

FXSD-busy The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for an FXSDN interface (ABCD = 1111).

FXOD-busy

PLAR3idle The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the idle state for

a PLAR D3 interface (ABCD = 0000).

PLAR3idle

PLAR3busy The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for an PLAR D3 interface (ABCD = 1111).

PLAR3busy

PLAR4idle The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the idle state for

a PLAR D4 interface (ABCD = 1111).

PLAR4idle

PLAR4busy The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for an PLAR D4 interface (ABCD = 0000).

PLAR4busy

DPO-idle The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the idle state for

a DPO interface (ABCD = 0000).

DPT-idle

DPO-busy The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for a DPO interface (ABCD = 1111).

DPT-busy

DPT-idle The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the idle state for

a DPT interface (ABCD = 0000).

DPO-idle

DPT-busy The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for a DPT interface (ABCD = 1111).

DPO-busy

USER-xxxx The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent a user-defined

pattern of ABCD = xxxx.

USER-xxxx

1

1

xxxx is the same value on both the Network and the DSX-1 sides.

Clearing Assignments

Clearing assignments sets all time slots to Unassgn (unassigned).

Main Menu →Configuration →Time Slot Assignment →Clear Assignments