365

Auxiliary Area Allocations Appendix D

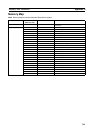

Data Shift Instructions

Note When a double-length operand is used, add 1 to the value shown in the length column in the above

table.

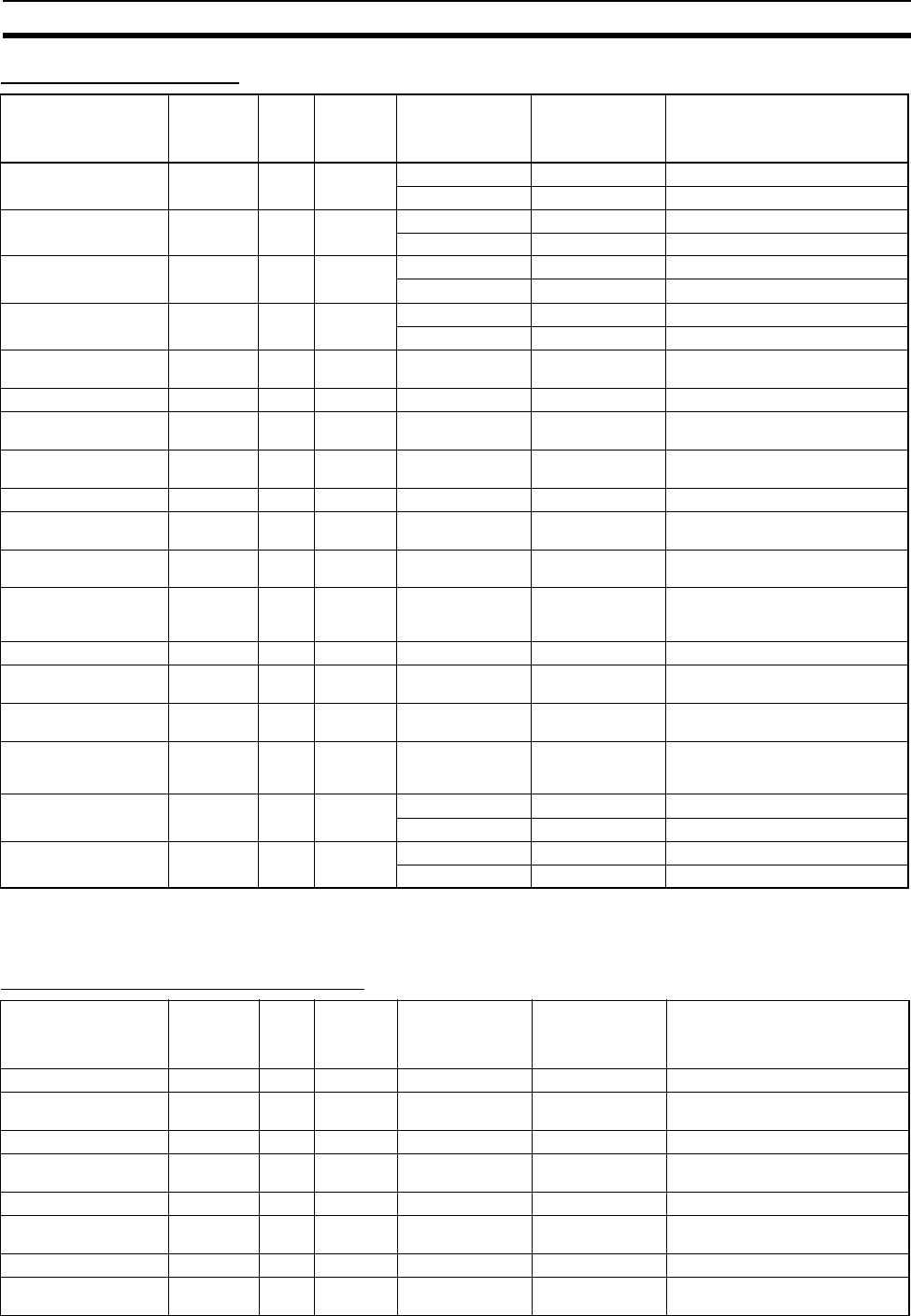

Increment/Decrement Instructions

Instruction Mnemonic Code Length

(steps)

(See

note.)

ON execution

time (

µs)

Hardware

implementation

Conditions

SHIFT REGISTER SFT 010 3 12.4 --- Shifting 1 word

368.1 --- Shifting 1,000 words

REVERSIBLE SHIFT

REGISTER

SFTR 084 4 14.0 --- Shifting 1 word

1.44 ms --- Shifting 1,000 words

ASYNCHRONOUS

SHIFT REGISTER

ASFT 017 4 13.9 --- Shifting 1 word

3.915 ms --- Shifting 1,000 words

WORD SHIFT WSFT 016 4 9.7 --- Shifting 1 word

728.1 --- Shifting 1,000 words

ARITHMETIC SHIFT

LEFT

ASL 025 2 0.45 Yes ---

DOUBLE SHIFT LEFT ASLL 570 2 0.80 Yes ---

ARITHMETIC SHIFT

RIGHT

ASR 026 2 0.45 Yes ---

DOUBLE SHIFT

RIGHT

ASRL 571 2 0.80 Yes ---

ROTATE LEFT ROL 027 2 0.45 Yes ---

DOUBLE ROTATE

LEFT

ROLL 572 2 0.80 Yes ---

ROTATE LEFT WITH-

OUT CARRY

RLNC 574 2 0.45 Yes ---

DOUBLE ROTATE

LEFT WITHOUT

CARRY

RLNL 576 2 0.80 Yes ---

ROTATE RIGHT ROR 028 2 0.45 Yes ---

DOUBLE ROTATE

RIGHT

RORL 573 2 0.80 Yes ---

ROTATE RIGHT WITH-

OUT CARRY

RRNC 575 2 0.45 Yes ---

DOUBLE ROTATE

RIGHT WITHOUT

CARRY

RRNL 577 2 0.80 Yes ---

ONE DIGIT SHIFT

LEFT

SLD 074 3 10.1 --- Shifting 1 word

1.208 ms --- Shifting 1,000 words

ONE DIGIT SHIFT

RIGHT

SRD 075 3 11.7 --- Shifting 1 word

1.775 ms --- Shifting 1,000 words

Instruction Mnemonic Code Length

(steps)

(See

note.)

ON execution

time (

µs)

Hardware

implementation

Conditions

INCREMENT BINARY ++ 590 2 0.45 Yes ---

DOUBLE INCRE-

MENT BINARY

++L 591 2 0.80 Yes ---

DECREMENT BINARY – – 592 2 0.45 Yes ---

DOUBLE DECRE-

MENT BINARY

– –L 593 2 0.80 Yes ---

INCREMENT BCD ++B 594 2 12.1 --- ---

DOUBLE INCRE-

MENT BCD

++BL 595 2 9.37 --- ---

DECREMENT BCD – –B 596 2 11.5 --- ---

DOUBLE DECRE-

MENT BCD

– –BL 597 2 9.3 --- ---