367

Auxiliary Area Allocations Appendix D

Note When a double-length operand is used, add 1 to the value shown in the length column in the above

table.

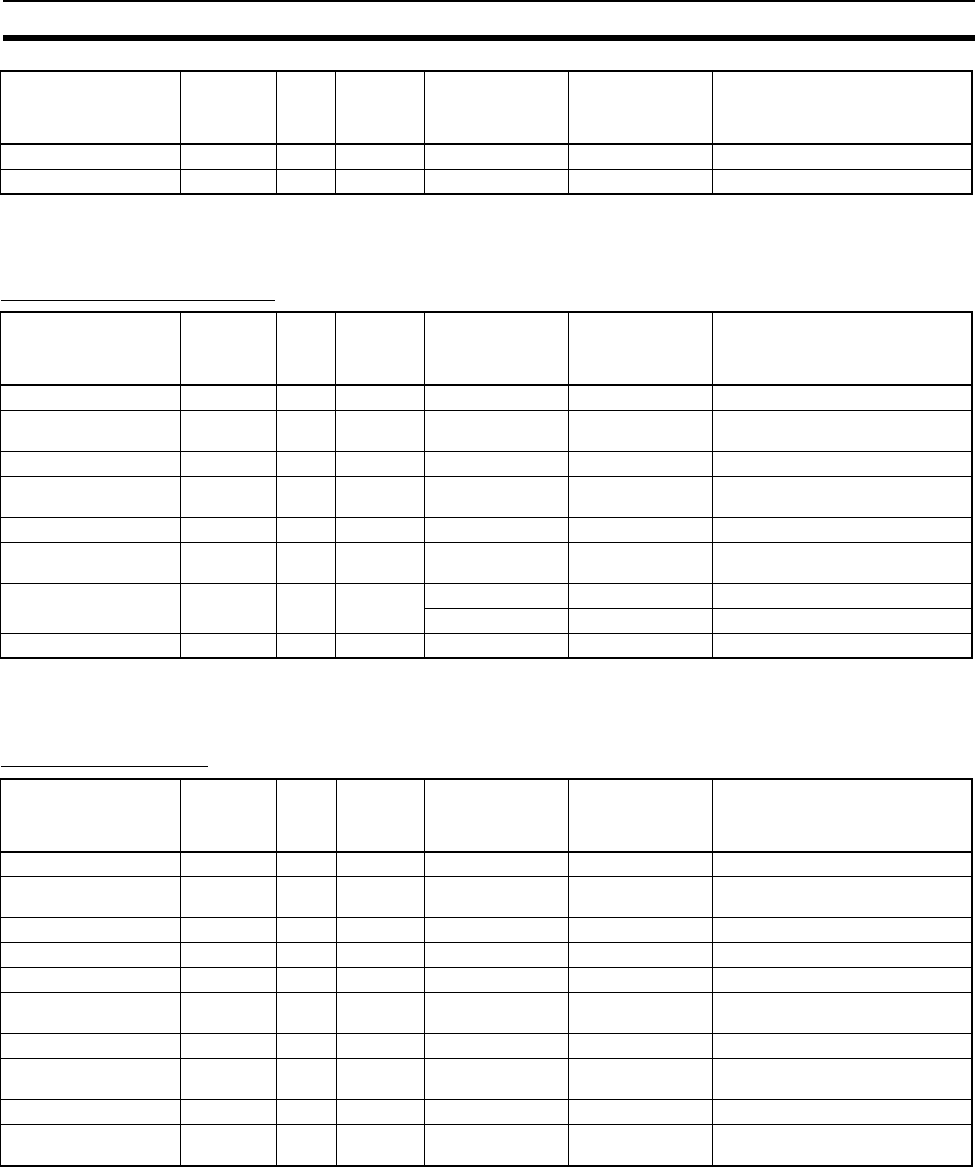

Conversion Instructions

Note When a double-length operand is used, add 1 to the value shown in the length column in the above

table.

Logic Instructions

Note When a double-length operand is used, add 1 to the value shown in the length column in the above

table.

BCD DIVIDE /B 434 4 18.3 --- ---

DOUBLE BCD DIVIDE /BL 435 4 26.7 --- ---

Instruction Mnemonic Code Length

(steps)

(See

note.)

ON execution

time (

µs)

Hardware

implementation

Conditions

BCD-TO-BINARY BIN 023 3 0.40 Yes ---

DOUBLE BCD-TO-

DOUBLE BINARY

BINL 058 3 7.4 --- ---

BINARY-TO-BCD BCD 024 3 8.0 --- ---

DOUBLE BINARY-TO-

DOUBLE BCD

BCDL 059 3 8.0 --- ---

2’S COMPLEMENT NEG 160 3 0.35 Yes ---

DOUBLE 2’S COM-

PLEMENT

NEGL 161 3 0.60 Yes ---

ASCII CONVERT ASC 086 4 11.8 --- Converting 1 digit into ASCII

18.1 --- Converting 4 digits into ASCII

ASCII TO HEX HEX 162 4 12.2 --- Converting 1 digit

Instruction Mnemonic Code Length

(steps)

(See

note.)

ON execution

time (

µs)

Hardware

implementation

Conditions

LOGICAL AND ANDW 034 4 0.30 Yes ---

DOUBLE LOGICAL

AND

ANDL 610 4 0.60 Yes ---

LOGICAL OR ORW 035 4 0.45 Yes ---

DOUBLE LOGICAL OR ORWL 611 4 0.60 Yes ---

EXCLUSIVE OR XORW 036 4 0.45 Yes ---

DOUBLE EXCLUSIVE

OR

XORL 612 4 0.60 Yes ---

EXCLUSIVE NOR XNRW 037 4 0.45 Yes ---

DOUBLE EXCLUSIVE

NOR

XNRL 613 4 0.60 Yes ---

COMPLEMENT COM 029 2 0.45 Yes ---

DOUBLE COMPLE-

MENT

COML 614 2 0.80 Yes ---

Instruction Mnemonic Code Length

(steps)

(See

note.)

ON execution

time (

µs)

Hardware

implementation

Conditions