155

Pulse Inputs Section 7-5

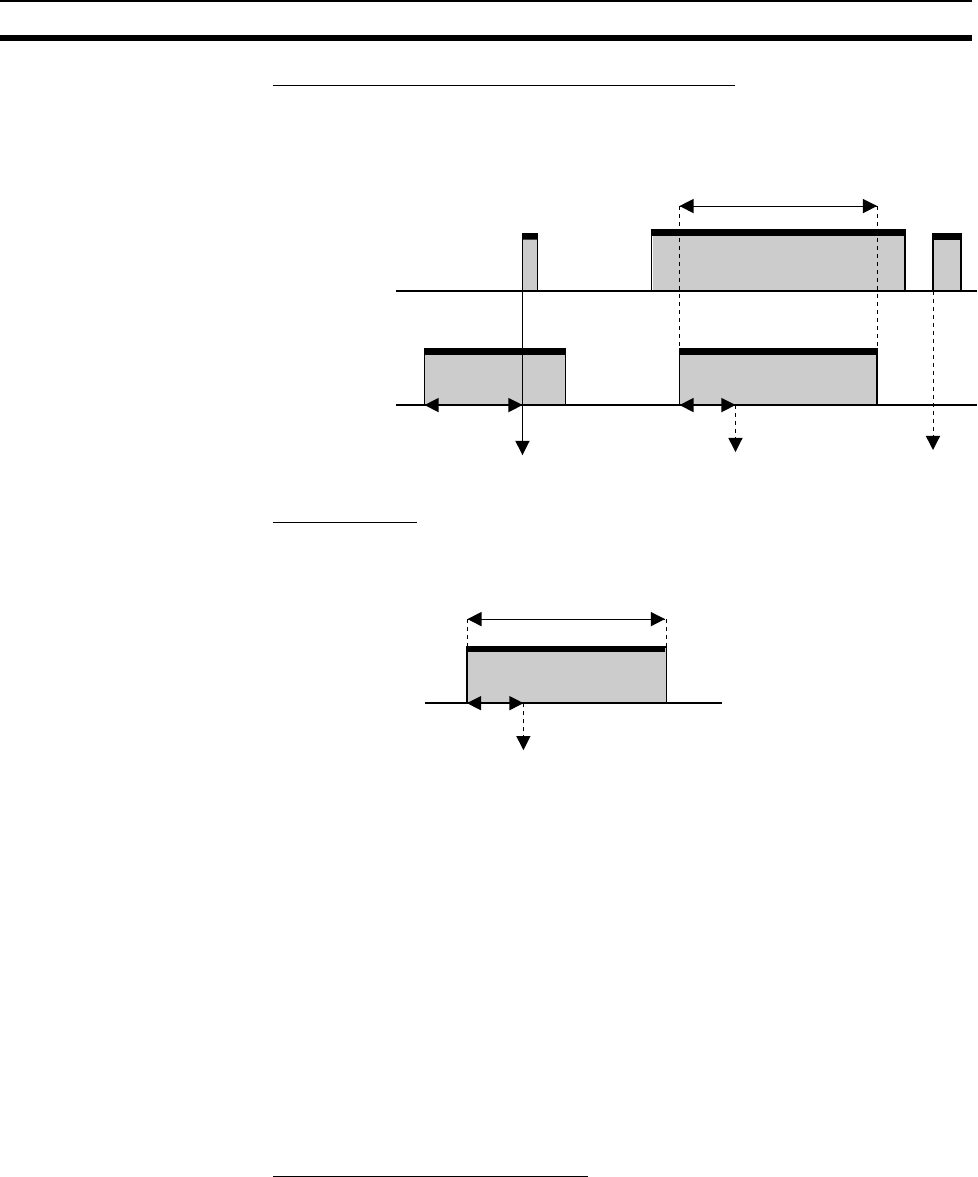

■ Phase-Z Signal (Reset Input) and Software Reset

The PV of the high-speed counter is reset on the first rising edge of the

phase-Z signal after the corresponding High-speed Counter Reset Bit (see

below) turns ON.

■ Software Reset

The PV is reset when the High-speed Counter Reset Bit turns ON. There are

separate Reset Bits for high-speed counters 1 and 2.

The High-speed Counter Reset Bits are as follows:

• High-speed Counter 1 Reset Bit: A610.01

• High-speed Counter 2 Reset Bit: A611.01

The High-speed Counter Reset Bits are refreshed only once each cycle, so a

Reset Bit must be ON for a minimum of 1 cycle to be read reliably.

Note The comparison table registration and comparison execution status will not be

changed even if the PV is reset. If a comparison was being executed before

the reset, it will continue.

Checking for High-speed

Counter Interrupts

The following two methods are available to check the PV of high-speed

counters 1 or 2.

• Target-value comparison method

• Range comparison method

■ Target-value Comparison Method

Up to 48 target values and corresponding interrupt task numbers can be reg-

istered in the comparison table. When the counter PV matches one of the 48

registered target values, the specified interrupt task will be executed.

Comparisons are made to each target value in the order that they appear in

the comparison table until all values have been met, and then comparison will

return to the first value in the table.

1 or more cycles

Within 1 cycle

1 or more cycles

Reset Reset by cycle. Not reset.

Phase-Z

(reset input)

Reset Bit for

High-speed

Counter 1 or 2

Within 1 cycle

1 or more cycles

Reset by cycle.

Reset Bit for

High-speed

Counter 1 or 2