2 - 13

2 MULTIPLE CPU SYSTEM

2.3 Communication between the PLC CPU and the Motion CPU in the Multiple CPU System

The following tasks can be performed between the PLC CPU and the Motion CPU in

the Multiple CPU system.

• Data transfer between CPUs by the automatic refresh function of the shared CPU

memory

• Control instruction from the PLC CPU to Motion CPU by the Motion dedicated

Instructions

• Reading/writing device data from the PLC CPU to Motion CPU by the dedicated

instruction

2.3.1 Automatic Refresh Function of The Shared CPU Memory

(1) Automatic refresh function of the shared CPU memory

(a) The automatic refresh function of the shared CPU memory is executed

automatically the data transfer between CPUs in the Multiple CPU system

during END processing in the PLC CPU or during main cycle processing

(free time except motion control) in the Motion CPU.

When the automatic refresh function is used, the data in the device memory

of the other CPU is read automatically, so the device data of other CPU can

be used as the device data of self CPU.

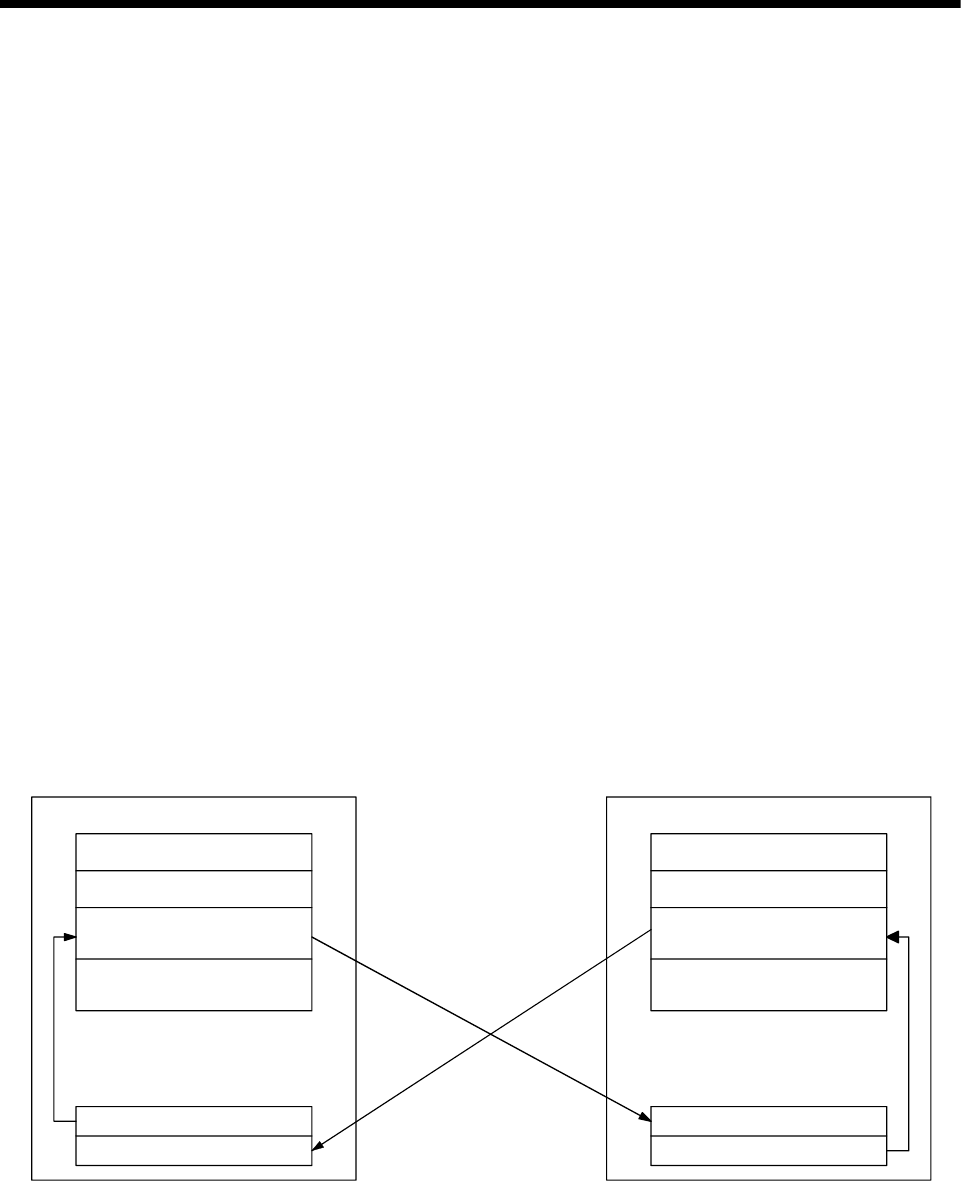

The diagram below illustrates the automatic refresh operation involving 32

points (B0 to B1F) for the PLC CPU of CPU No.1 and 32 points (B20 to

B3F) for the Motion CPU of CPU No.2.

Self CPU operation data area

System area

Automatic refresh area

CPU No.1 (PLC CPU)

User-defined area

Shared CPU memory

Device memory

B0 to B1F (CPU No.1)

B20 to B3F (CPU No.2)

CPU No.2 (Motion CPU)

3) Reading via main cycle

processing of CPU No.2

4) Reading via END

processing of CPU No.1

1) Written via END processing

of CPU No.1

2) Written via main cycle processing

of CPU No.2

Self CPU operation data area

System area

Automatic refresh area

User-defined area

Shared CPU memory

Device memory

B0 to B1F (CPU No.1)

B20 to B3F (CPU No.2)

Processing details of CPU No.1 (PLC CPU) at the END processing.

1) : Data of transmitting devices B0 to B1F for CPU No.1 is transferred to the

automatic refresh area of shared memory in the self CPU.

4) : Data in the automatic refresh area of shared memory in CPU No.2 is

transferred to B20 to B3F in the self CPU.