2 - 13

2 MULTIPLE CPU SYSTEM

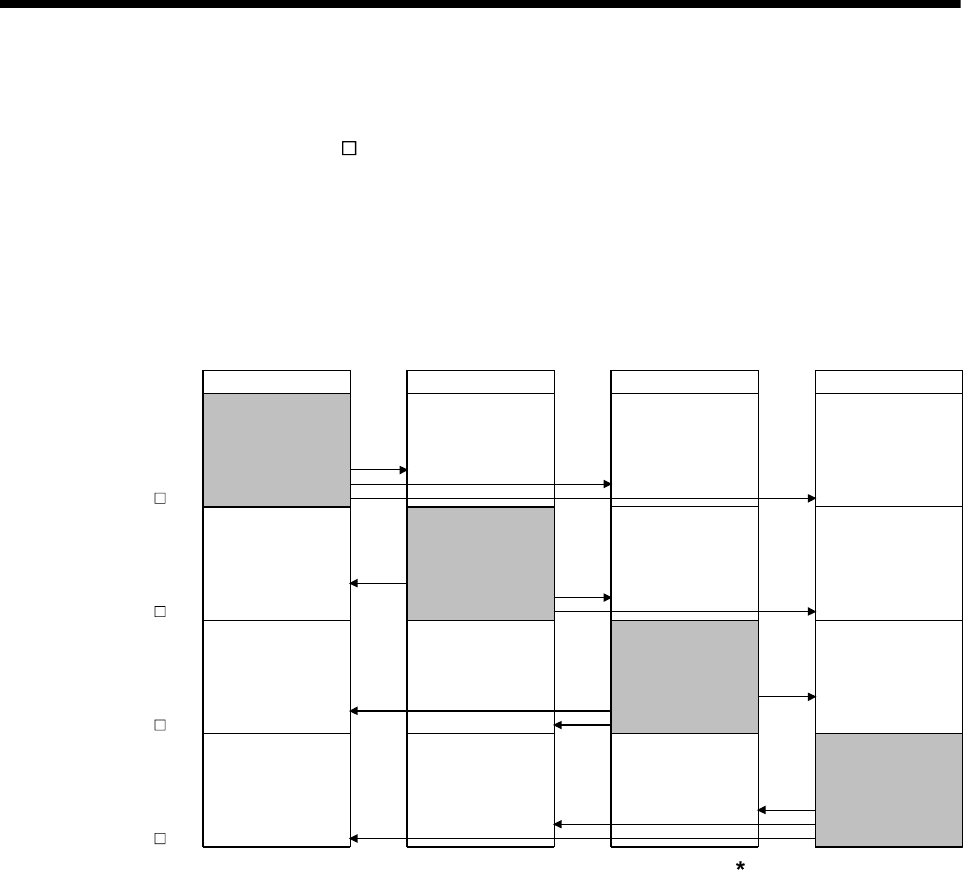

(d) Multiple CPU high speed transmission area

The area corresponding to the Multiple CPU high speed main base unit

(Q3

DB) and Multiple CPU high speed transmission that uses the drive

system controllers including QnUD(H)CPU and Motion CPU.

The image chart of Multiple CPU high speed transmission area is shown

below.

Refer to Section 2.3.2(1) for access to the Multiple CPU high speed

transmission area of self CPU and other CPU.

CPU No.1

Multiple CPU high

speed transmission

area

(Reception)

CPU No.1

Multiple CPU high

speed transmission

area

(Reception)

CPU No.2

to

(Note-1)

U3E0\G

U3E0\G10000

to

(Note-1)

U3E1\G

U3E1\G10000

to

(Note-1)

U3E2\G

U3E2\G10000

to

(Note-1)

U3E3\G

U3E3\G10000

CPU No.4

Multiple CPU high

speed transmission

area

(Reception)

CPU No.3

Multiple CPU high

speed transmission

area

(Reception)

CPU No.2

Multiple CPU high

speed transmission

area

(Reception)

CPU No.1

CPU No.2

Multiple CPU high

speed transmission

area

(Reception)

CPU No.3 CPU No.4

CPU No.1

Multiple CPU high

speed transmission

area

(Transmission)

(Note-2)

CPU No.2

Multiple CPU high

speed transmission

area

(Transmission)

(Note-2)

CPU No.3

Multiple CPU high

speed transmission

area

(Transmission)

(Note-2)

CPU No.4

Multiple CPU high

speed transmission

area

(Transmission)

(Note-2)

CPU No.1

Multiple CPU high

speed transmission

area

(Reception)

CPU No.4

Multiple CPU high

speed transmission

area

(Reception)

CPU No.3

Multiple CPU high

speed transmission

area

(Reception)

CPU No.4

Multiple CPU high

speed transmission

area

(Reception)

CPU No.3

Multiple CPU high

speed transmission

area

(Reception)

CPU No.2

Multiple CPU high

speed transmission

area

(Reception)

(Note-1) : The final device is "10000+(A 1024-B-1)".

A : Data transmission size of each CPU (1k words in unit)

B : Size used in the automatic refresh of each CPU.

Refer to Section "2.3.2 Multiple CPU high speed transmission"

for the size setting of A and B.

(Note-2) : Transmission area to write/read in the self CPU.

Reception area from the other CPU can be read only.

It is updated ever

y

0.88ms.