2 - 14

2 MULTIPLE CPU SYSTEM

2.3.2 Multiple CPU high speed transmission

(1) Multiple CPU high speed transmission

Multiple CPU high speed transmission is a function for fixed cycle data

transmission between Multiple CPUs (Multiple CPU high speed transmission

cycle is 0.88ms.).

Secure data transmission is possible without effecting the PLC CPU scan time or

Motion CPU main cycle because the data transmission and execution of PLC

program and Motion SFC program can be executed with parallel processing.

High speed response between multiple CPUs is realized by synchronizing the

Multiple CPU high speed transmission cycle with Motion CPU operation cycle.

The following methods of data transmission exist between Multiple CPUs for

Multiple CPU high speed transmission.

• Multiple CPU area device method

Directly set the Multiple CPU high speed transmission area by Multiple CPU

area device (U

\G ) in the program.

• Automatic refresh method

Refresh the internal devices of each CPU by automatic refresh via "Multiple

CPU high speed transmission area".

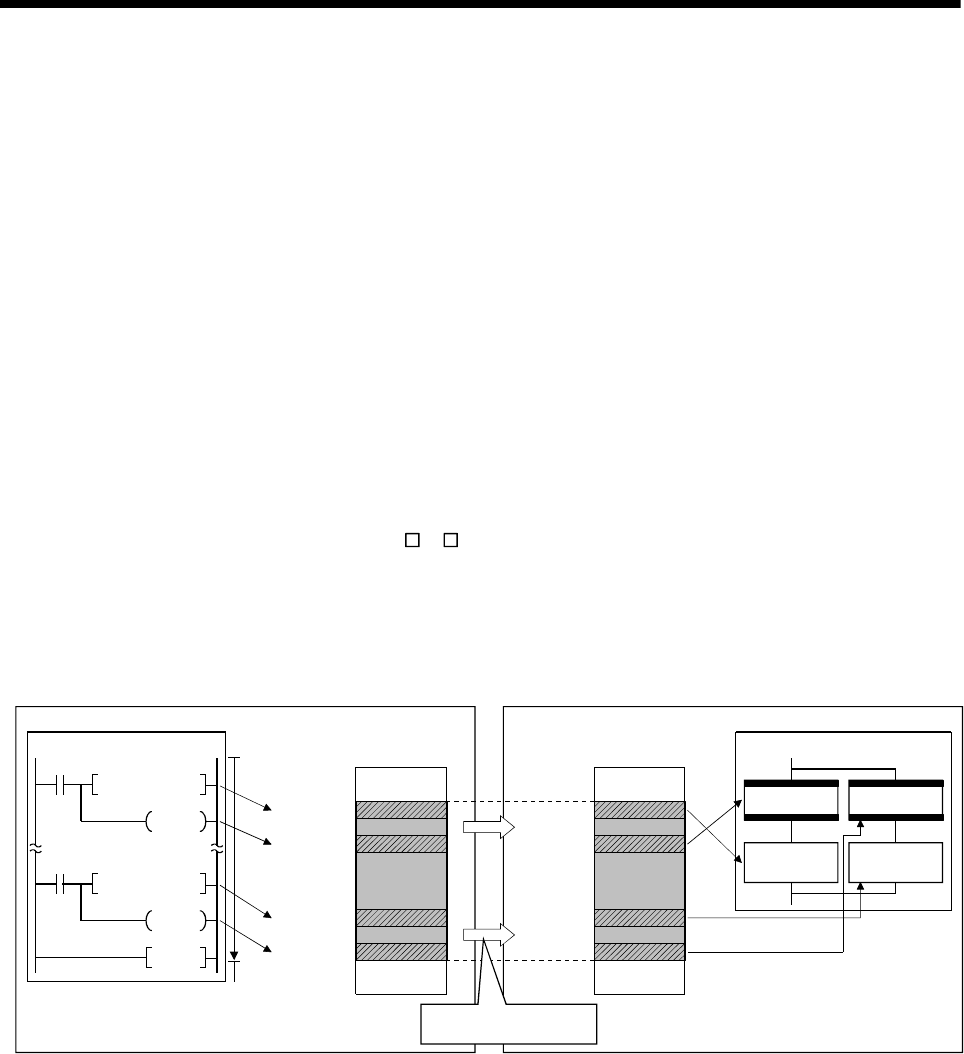

(a) Multiple CPU area device method

CPU shared memory

(User setting area

(Note-1)

)

SM400

U3E0\

G10110.5

MOV W1

U3E0\

G10100

SM400

2)

U3E0\G10000

U3E0\G10010

U3E0\G10100

U3E0\G10110

U3E0\G10000

U3E0\G10010

U3E0\G10100

U3E0\G10110

5)

1)

4)

U3E0\

G10010.1

MOV W0

U3E0\

G10000

END

CPU No.1 (PLC CPU) CPU No.2 (Motion CPU)

CPU shared memory

(User setting area

(Note-1)

)

PLC program Motion SFC program

3)

6)

G0

U3E0\G10010.1

F0

W0=U3E0\G10010

G1

U3E0\G10110.5

F1

W1=U3E0\G10110

CPU No.1

transmitting

data

CPU No.1

transmitting

data

Multiple CPU high speed

transmission in 0.88ms cycle

1), 4) : Write data in the user setting area

(Note-1)

by the instruction that uses the Multiple CPU area device.

3), 6) : Read data from the user setting area

(Note-1)

by the instruction that uses the Multiple CPU area device.

2), 5) : Transmit the contents of user setting area

(Note-1)

to the other CPU with by Multiple CPU high speed transmission in 0.88ms cycle.

Note-1: The area composed in the Multiple CPU high speed transmission area.

(Refer to Section "(3) Memory configuration of Multiple CPU high speed transmission area".)