APP - 34

A

PPENDICES

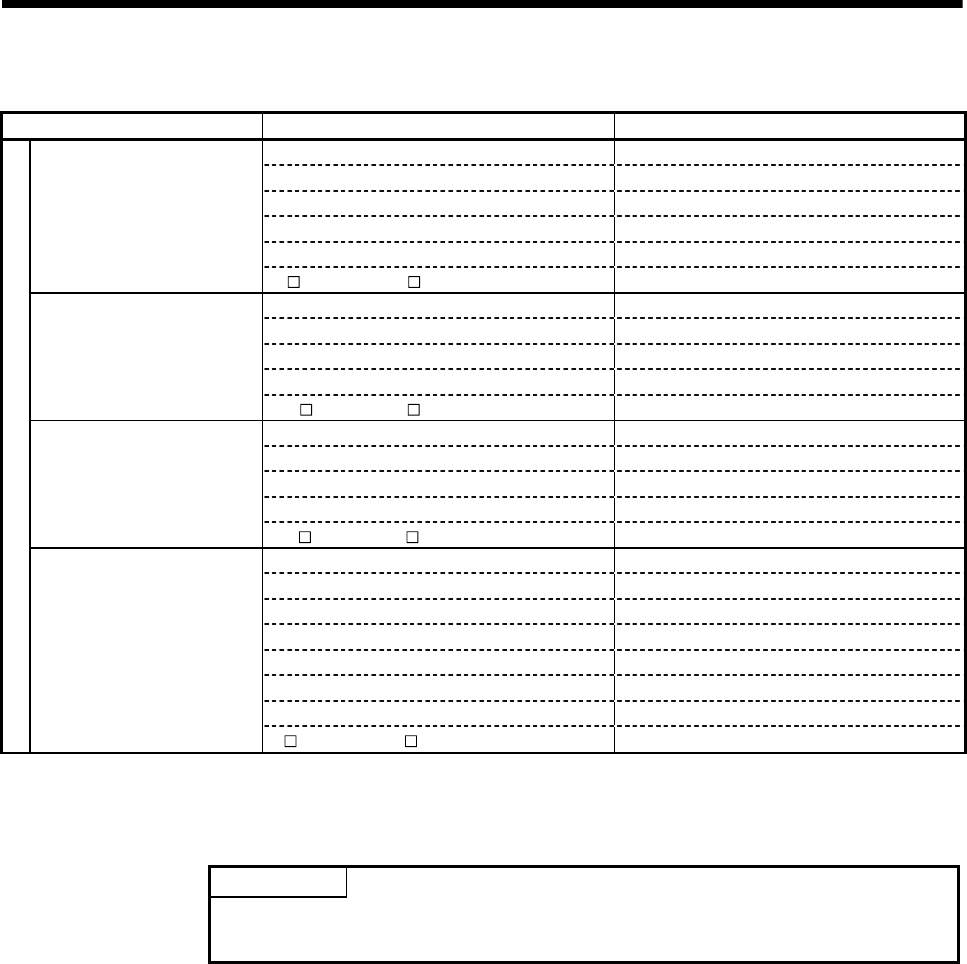

Table 4.8 Other devices list (Continued)

Item Q173DCPU/Q172DCPU Q173HCPU/Q172HCPU

X0 to X1FFF X0 to X1FFF

Y0 to Y1FFF Y0 to Y1FFF

M0 to M8191 M0 to M8191

— L0 to L8191

B0 to B1FFF B0 to B1FFF

Output device

U \G10000.0 to U \G(10000 + p –1).F

(Note-2)

—

D0 to D8191 D0 to D8191

W0 to W1FFF W0 to W1FFF

#0 to #7999 #0 to #8191

Absolute value address Absolute value address

Watch data

U

\G10000 to U \G(10000 + p –1)

(Note-2)

—

D0 to D8191 D0 to D8191

W0 to W1FFF W0 to W1FFF

#0 to #7999 #0 to #8191

Constant (Hn/Kn)

(Note-3)

Constant (Hn/Kn)

(Note-3)

ON region setting

U

\G10000 to U \G(10000 + p – 1)

(Note-2)

—

X0 to X1FFF X0 to X1FFF

Y0 to Y1FFF Y0 to Y1FFF

M0 to M8191 M0 to M8191

— L0 to L8191

B0 to B1FFF B0 to B1FFF

F0 to F2047 F0 to F2047

SM0 to SM1999 M9000 to M9255

Limit switch output data

Output enable/disable bit

Forced output bit

U

\G10000.0 to U \G(10000 + p – 1).F

(Note-2)

—

(Note-2) : "p" indicates the user setting area points of Multiple CPU high speed transmission area in each CPU.

(Note-3) : Setting range varies depending on the setting units.

POINT

Refer to Chapter 2 for number of user setting area points of Multiple CPU high

speed transmission area.