90 Xilinx Development System

Xilinx System Generator v2.1 Reference Guide

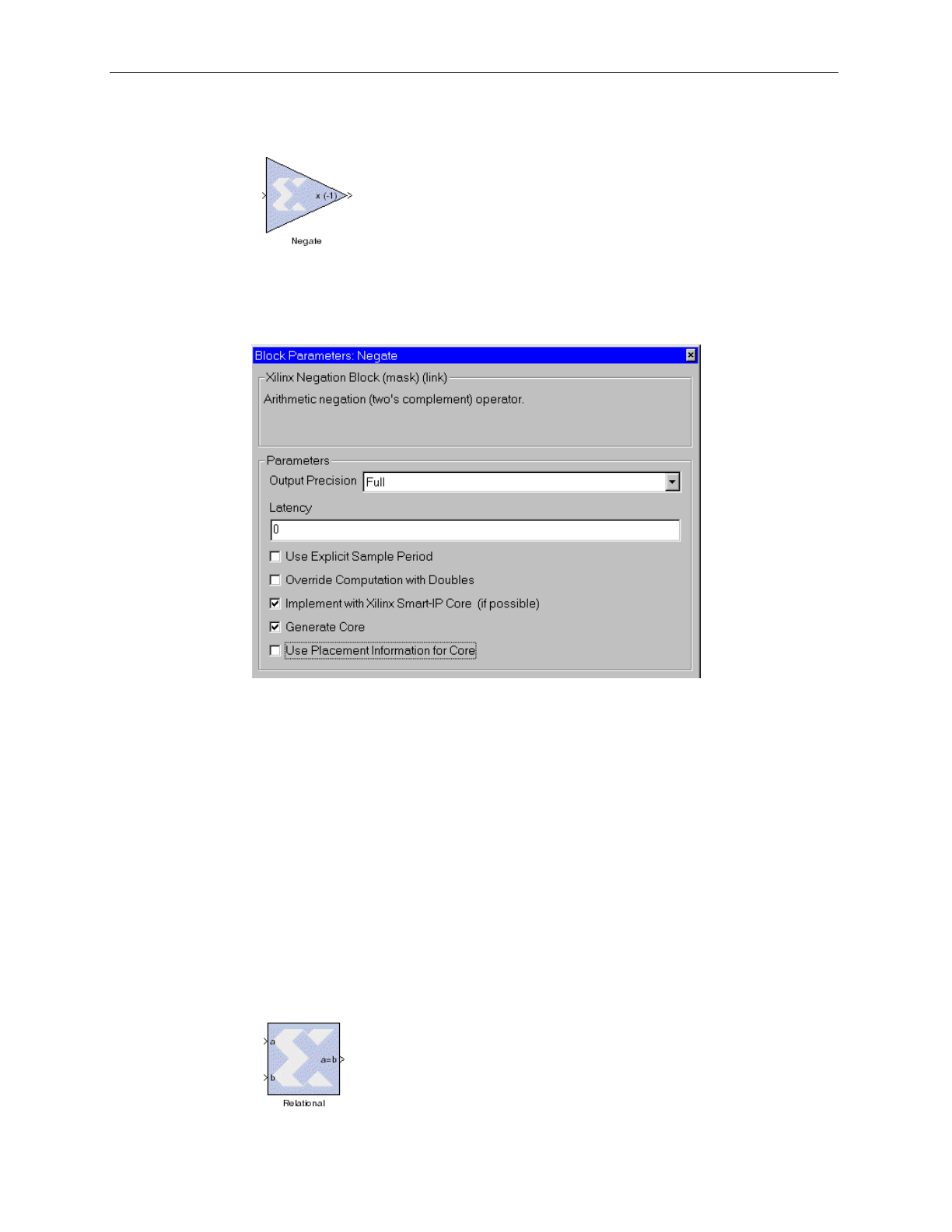

Negate

The Xilinx Negate block computes the arithmetic negation (two’s

complement) of its input.

The block can be implemented either as a Xilinx LogiCORE or as a

synthesizable VHDL module.

Block Parameters Dialog Box

The block parameters dialog box can be invoked by double-clicking the icon in your

Simulink model.

Figure 3-61: Negate block parameters dialog box

Parameters used by this block are explained in the Common Parameters section of the

previous chapter.

Xilinx LogiCORE

If the Implement with Xilinx Smart-IP Core checkbox is selected and the

input width is between 1 and 256, inclusive, the block uses the Xilinx LogiCORE Twos

Complementer V5.0. Otherwise, the block is implemented as a synthesizable VHDL

module.

The Core datasheet can be found on your local disk at:

%XILINX%\coregen\ip\xilinx\eip1\com\xilinx\ip\baseblox_v5_0\do

c\twos_comp.pdf

Relational

The Xilinx Relational block implements a comparator. The supported

comparisons are the following: