State Machine 119

Xilinx Blocks

Xilinx LogiCORE

This block uses Version 3.2 of the Xilinx Single Port Block Memory LogiCORE and

Version 5.0 of the Xilinx Distributed RAM LogiCORE.

The Core datasheet for the Single Port Block Memory may be found locally at:

%XILINX%\coregen\ip\xilinx\eip1\com\xilinx\ip\blkmemsp_v3_2\do

c\sp_block_mem.pdf

The Core datasheet for the Distributed Memory may be found on your local disk at:

%XILINX%\coregen\ip\xilinx\eip1\com\xilinx\ip\c_dist_mem_v5_0\

doc\dist_mem.pdf

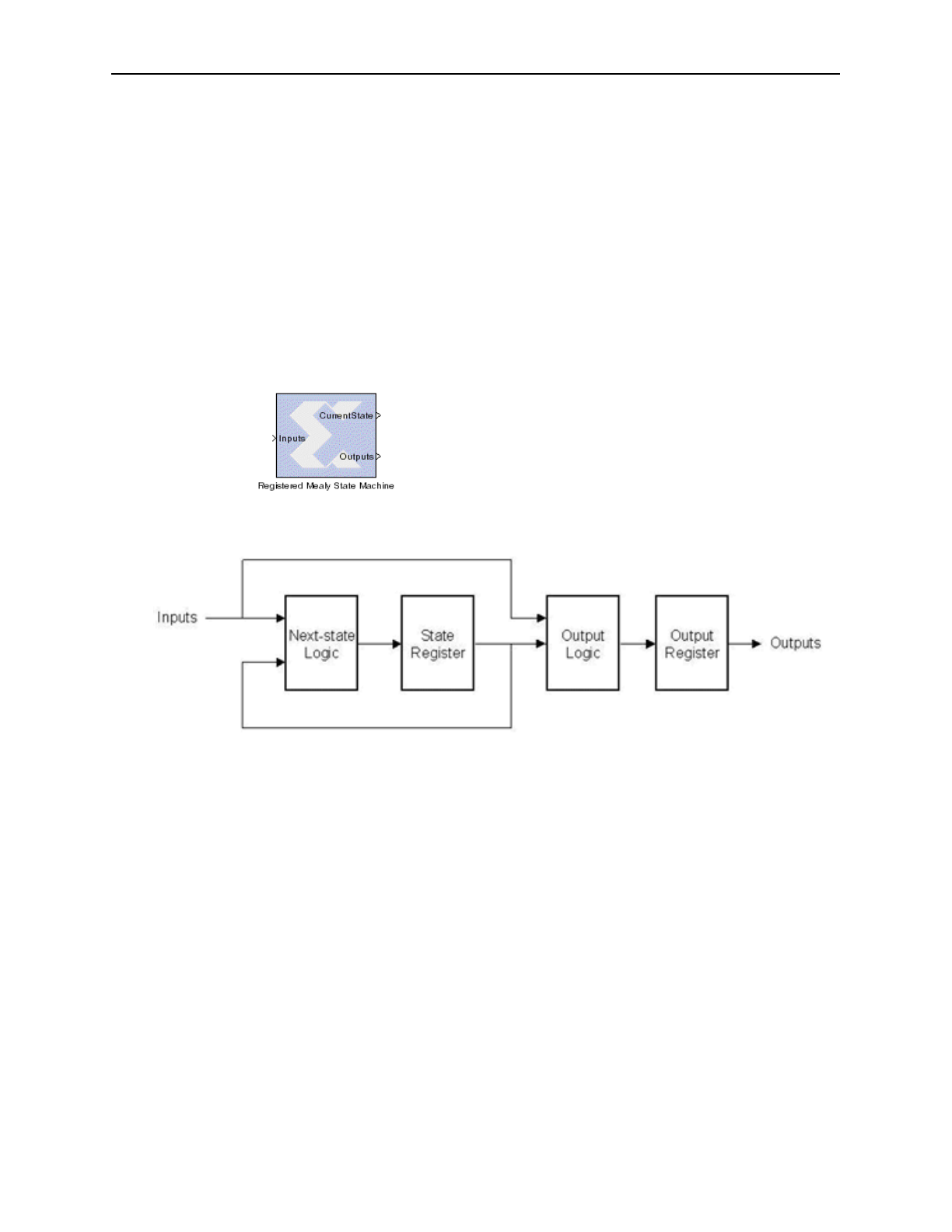

Registered Mealy State Machine

The Xilinx Registered Mealy State Machine block implements

a state machine whose output depends on both the current

state and input. This block is like the Mealy State Machine

block, except that its output logic is registered.

A block diagram of this type of state machine is shown below:

Figure 3-84: Registered Mealy State Machine block diagram

The block is configured by providing next state and output matrices. These matrices

are defined by the state machine’s next state/output table. For example, consider the

problem of designing a state machine to recognize the pattern ’1011’ within a serial