106 Xilinx Development System

Xilinx System Generator v2.1 Reference Guide

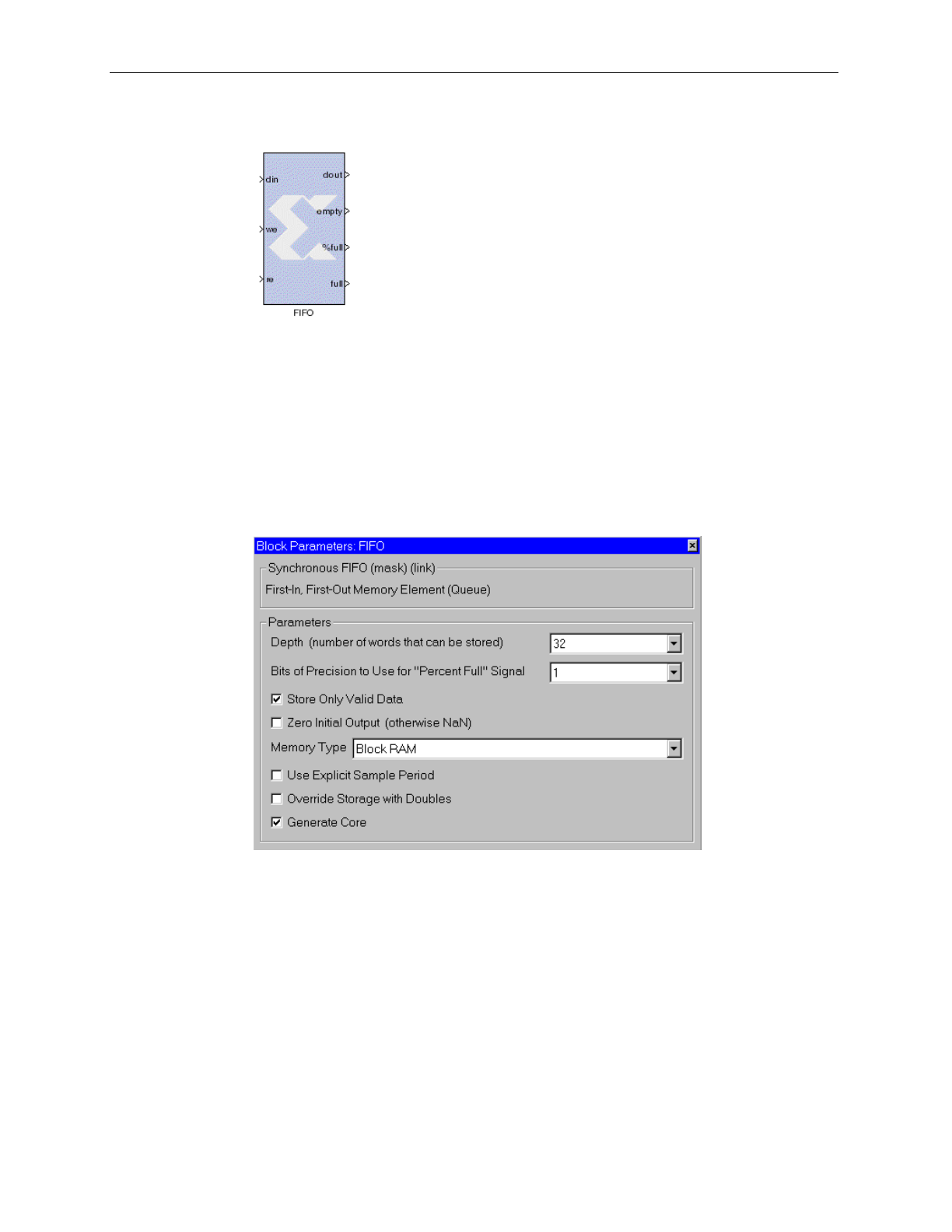

FIFO

The Xilinx FIFO block implements a First-In-First-Out memory

queue.

Values presented at the module’s data-input port is written to the

next available empty memory location when the write-enable input

is one. The memory full status output port is assserted to one when

no unused locations remain in the module’s internal memory. The

percent full output port indicates the percentage of internal memory

in use, represented with user-specified precision. By asserting the

read-enable input port, data can be read out of the FFO via the data

output port (dout) in the order in which they were written. The

memory-empty status output (empty) indicates that no more data reside in the

memory.

The FIFO can be implemented either using distributed or block RAM. If distributed

memory is selected, the maximum depth of the FIFO is 256. If block RAM is used, the

maximum depth is 64K words.

Block Parameters Dialog Box

The block parameters dialog box can be invoked by double-clicking the icon in your

Simulink mode.

Figure 3-72: FIFO block parameters dialog box

Parameters specific to the FIFO block are:

• Depth: specifies the number of words that can be stored.

• Bits of Precision to Use for Percent Full Signal: specifies the

number of bits that will be output from the %full port. The binary point for this

unsigned output is always at the top of the word. Thus, if the Bits of

Precision is set to one, the output can take on two values: 0.0 and 0.5, the latter

indicating that the FIFO is at least 50% full. Given two bits of precision, the

possible output values are 0.00, 0.25, 0.50 and 0.75.