Communication 57

Xilinx Blocks

When the branch lengths are specified as an array, the block operates the same in

either interleaver or deinterleaver mode because the array fully defines the length of

all the branches. The array must have length B, matching the number of branches.

The reset pin (rst) will set the commutator arms to branch 0, but will not clear the

branches of data.

Block Interface

The Interleaver/Deinterleaver block has two input and one output ports. The input

port, din, must be between 1 and 256 (inclusive) bits. The reset port, rst, must be of

type UFix1_0. The size of the output port, dout, is the same as the input port, din.

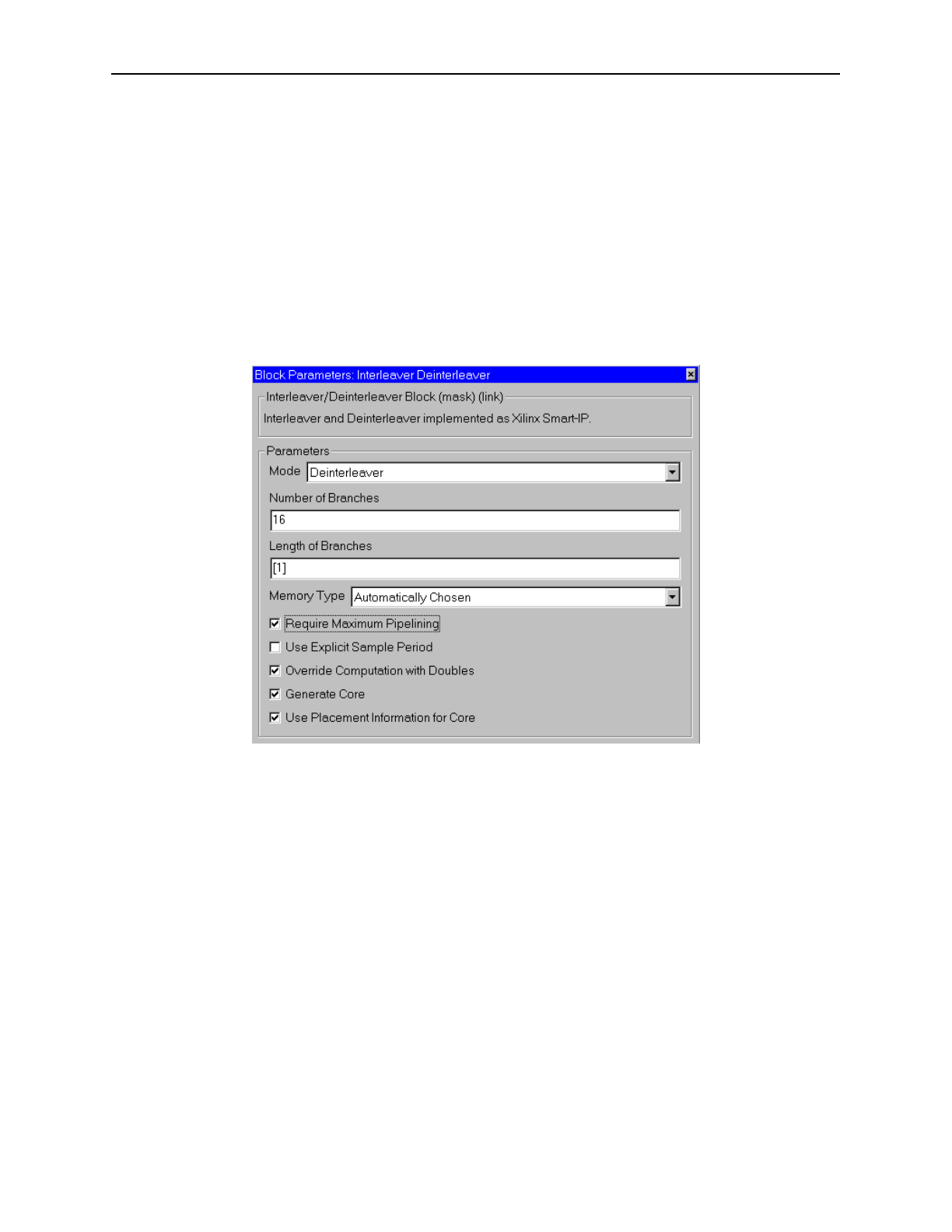

Block Parameters Dialog Box

Figure 3-36: Interleaver/Deinterleaver block parameters dialog box

Parameters specific to the block are:

• Mode: Interleaver or Deinterleaver

• Number of Branches: 1 to 256 (inclusive)

• Length of Branches: 1 to MAX (inclusive). MAX depends on the number of

branches and size of core input. Branch length must be an array of either length

one or number of branches. If the array size is one, the value is used as a constant

difference between consecutive branches. Otherwise, each branch has a unique

length.

• Memory Type: Automatically chosen, block RAM or distributed RAM

Other parameters used by this block are described in the Common Parameters section

of the previous chapter.

Xilinx LogiCORE

The block always uses the Xilinx LogiCORE: Interleaver/Deinterleaver v1.1.