112 Xilinx Development System

Xilinx System Generator v2.1 Reference Guide

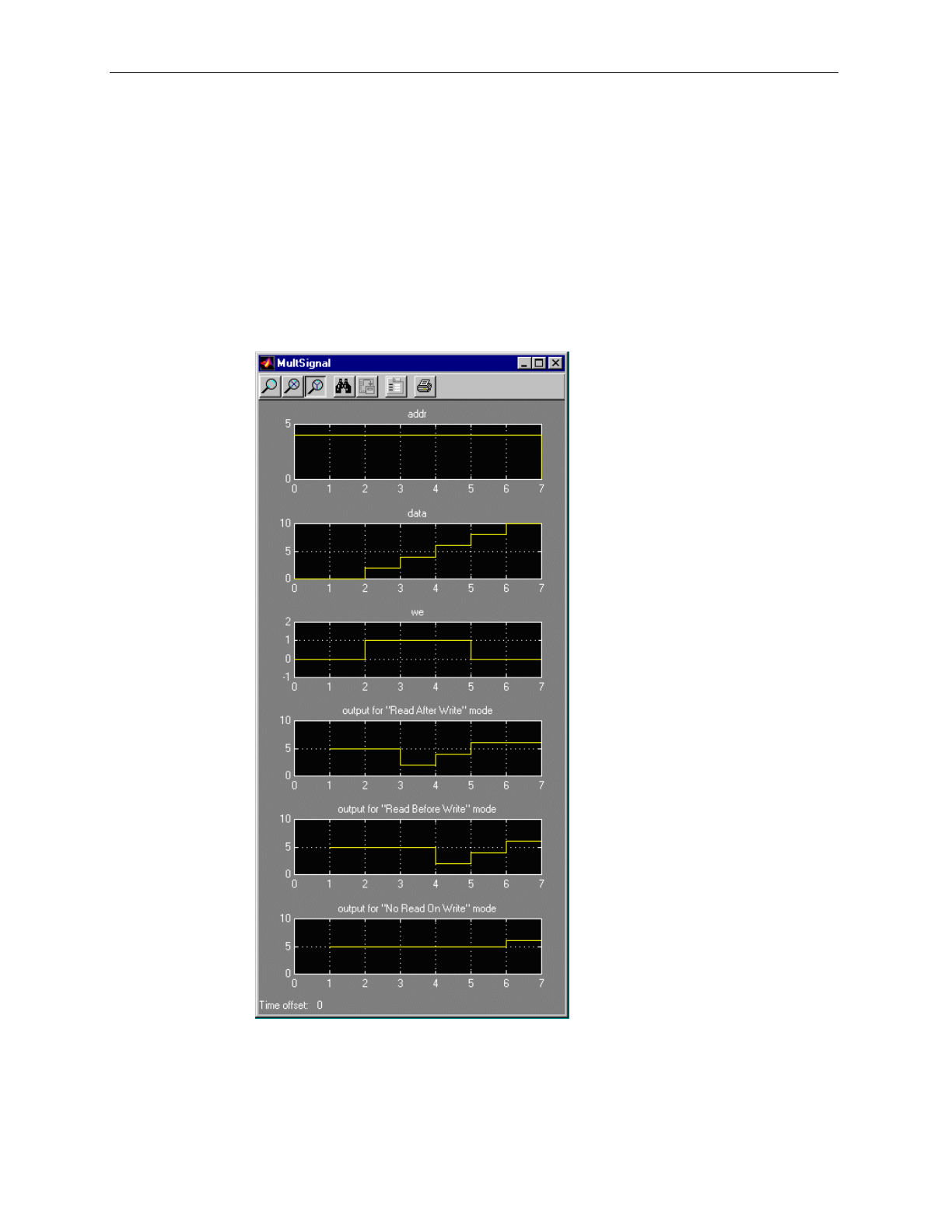

• Read After Write

• Read Before Write

• No Read On Write

The write modes can be described with the help of the figure shown below. In the

figure the memory has been set to an initial value of 5 and the address bit is specified

as 4. When using No Read On Write mode, the output is unaffected by the address line

and the output is the same as the last output when the WE was 0. For the other two

modes, the output is obtained from the location specified by the address line, and

hence is the value of the location being written to. This means that the output can be

either the old value (Read Before Write mode), or the new value (Read After Write

mode).

Figure 3-75: Illustration of write modes

Virtex, Virtex-E, and Spartan-II FPGA families support only Read After Write mode.

Virtex-II supports all modes.