134 Xilinx Development System

Xilinx System Generator v2.1 Reference Guide

The division of the design into parts, and the speed at which each part must run, are

specified in the constraints file using multicycle path constraints. The example below

shows how this is done.

IOB Timing and Placement Constraints

When translated into hardware, System Generator’s Gateway In and Gateway Out

blocks become input and output ports. The locations of these ports and the speeds at

which they must operate can be entered in the Gateway In and Out configuration

GUIs. Please see the descriptions of the Gateway In block and the Gateway Out block

in the MATLAB I/O library section for more information.

Port location and speed are specified in the constraints file by IOB timing and

placement constraints. The following example shows the details

Example for showing constraints use

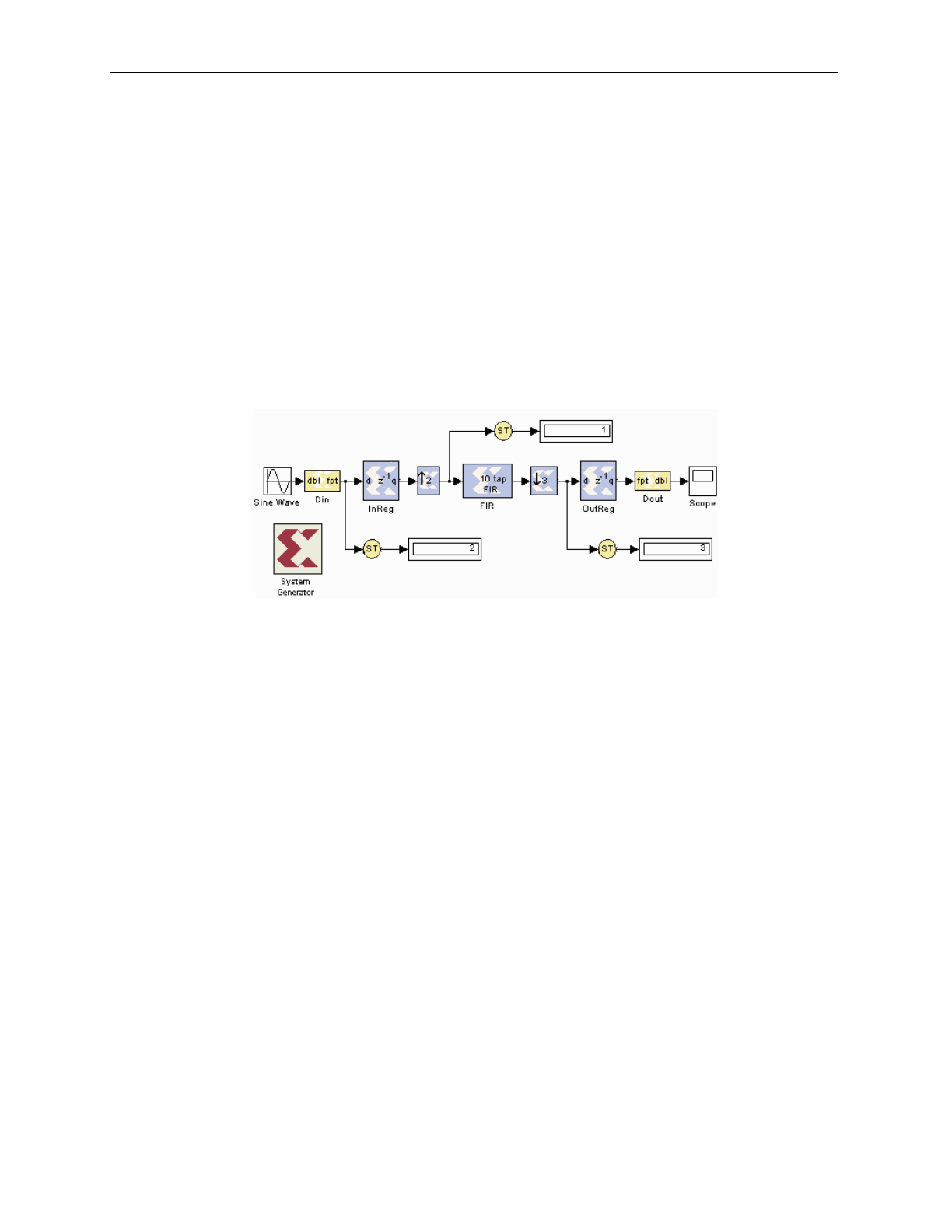

Figure 4-4: Example of a multirate design

The up sampler doubles the sample rate, and the down sampler divides the sample

rate by three. In this design, the system clock period is 10 ns (specified in the

parameters dialog box for the System Generator block), so the clock periods are 10 ns

for the FIR, 20 ns for the input register, and 30 ns for the output register. Shown below

are the constraints that carry this information.

Here are the lines from the ucf file that indicate the system clock period is 10 ns.

# Global period constraint

NET "clk" TNM_NET = "clk";

TIMESPEC "TS_clk" = PERIOD "clk" 10.0 ns HIGH 50 %;

To build the timing constraints, the blocks in the design are partitioned into timing

groups. Two blocks are in the same timing group if and only if they run at the same

sample rate. In this design the timing groups are named ce1_group, ce2_group, and

ce3_group.

The FIR block runs at the system rate and therefore goes into the ce1_group. The

logic used to generate clocks always runs at the system rate and is therefore in the

ce1_group as well. The constraints for the ce1_group are the following.

# ce1_group and inner group constraint

INST "FIR" TNM = "ce1_group";

INST "clock_driver_1" TNM = "ce1_group";

TIMESPEC "TS_ce1_group_to_ce1_group" = FROM "ce1_group" TO

"ce1_group" "TS_clk" * 1;