52 Xilinx Development System

Xilinx System Generator v2.1 Reference Guide

Communication

The blocks in the Communication library implement functions used in digital

communications systems, including convolutional and block channel coding,

interleaving, and utility functions.

Convolutional Encoder

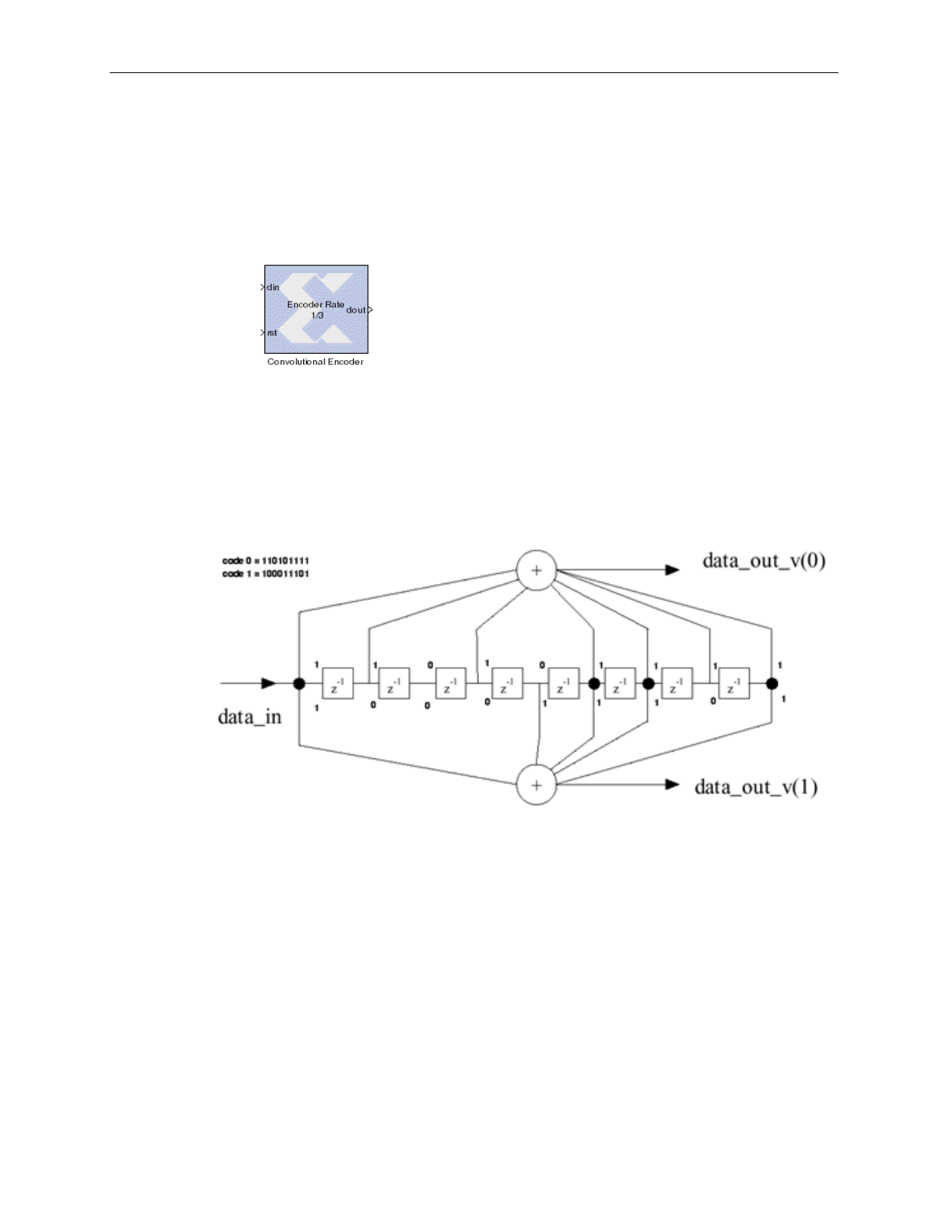

The Xilinx Convolutional Encoder block implements an encoder

for convolutional codes. Commonly used in tandem with a

Viterbi decoder block, this block can be used to implement

forward error correction (FEC) circuitry for digital

communication systems.

Data is encoded using a linear feed forward shift register to

compute modulo-two sums over a sliding window of input

data, as shown in the figure below. The length of the shift register, and the code's

constraint length, is equal to the length of the convolution codes that characterize the

encoder, specified in the block’s parameters dialog box. These convolution codes

specify which bits in the data window contribute to the modulo-two sum at the

encoder output. Resetting the block will clear the contents of the shift register to all

zeros. The encoder rate is the ratio of input bits to output bits, so a rate 1/2 encoder

outputs two bits for each input bit. Similarly, a rate 1/3 encoder outputs three bits for

each input bit.

Figure 3-30: Constraint length 9 convolutional encoder

Block Interface

The block has two input and one output ports. The input ports, din and rst, are

limited to type UFix1_0. The size of the output port, dout, is determined by the

output rate. The port will be either type UFix2_0 or UFix3_0.