126 Xilinx Development System

Xilinx System Generator v2.1 Reference Guide

where

N

s

= total number of next state logic block RAM bits

k =

d

s

= depth of state logic block RAM

w

s

= width of state logic block RAM

s = number of states

i = number of input bits

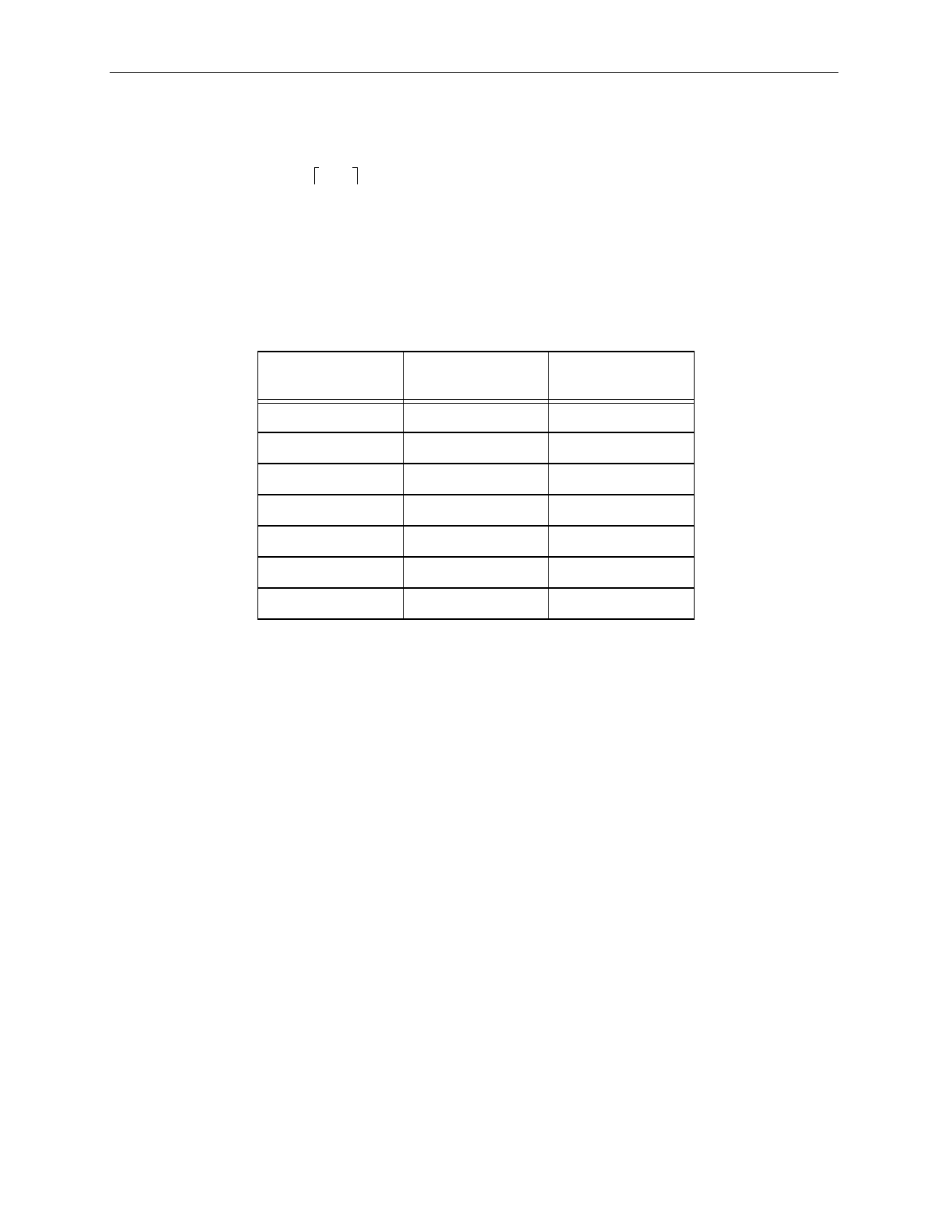

The following table gives examples of Block RAM sizes necessary for various state

machines:

Xilinx LogiCORE

This block uses Version 3.2 of the Xilinx Single Port Block Memory LogiCORE.

The block RAM width and depth limitations are described in the core datasheet for

the Single Port Block Memory, which may be found locally at:

%XILINX%\coregen\ip\xilinx\eip1\com\xilinx\ip\blkmemsp_v3_2\do

c\sp_block_mem.pdf

Number of States Number of

Input Bits

Block RAM Bits

Needed

2564

418

8 6 1536

16 5 2048

32 4 2560

52 1 768

100 4 14336

s

2

log