114 Xilinx Development System

Xilinx System Generator v2.1 Reference Guide

%XILINX%\coregen\ip\xilinx\eip1\com\xilinx\ip\blkmemsp_v3_2\do

c\sp_block_mem.pdf

The Core datasheet for the Distributed Memory can be found on your local disk at:

%XILINX%\coregen\ip\xilinx\eip1\com\xilinx\ip\c_dist_mem_v5_0\

doc\dist_mem.pdf

State Machine

The State Machine library provides a method for implementing Mealy and Moore

state machines. These state machines are implemented using block and distributed

RAMs, resulting in a very fast and efficient implementation. For example, a state

machine with 8 states, 1 input, and 2 outputs that are registered can be realized with a

single block RAM that runs at more than 150 MHz in a Xilinx Virtex device.

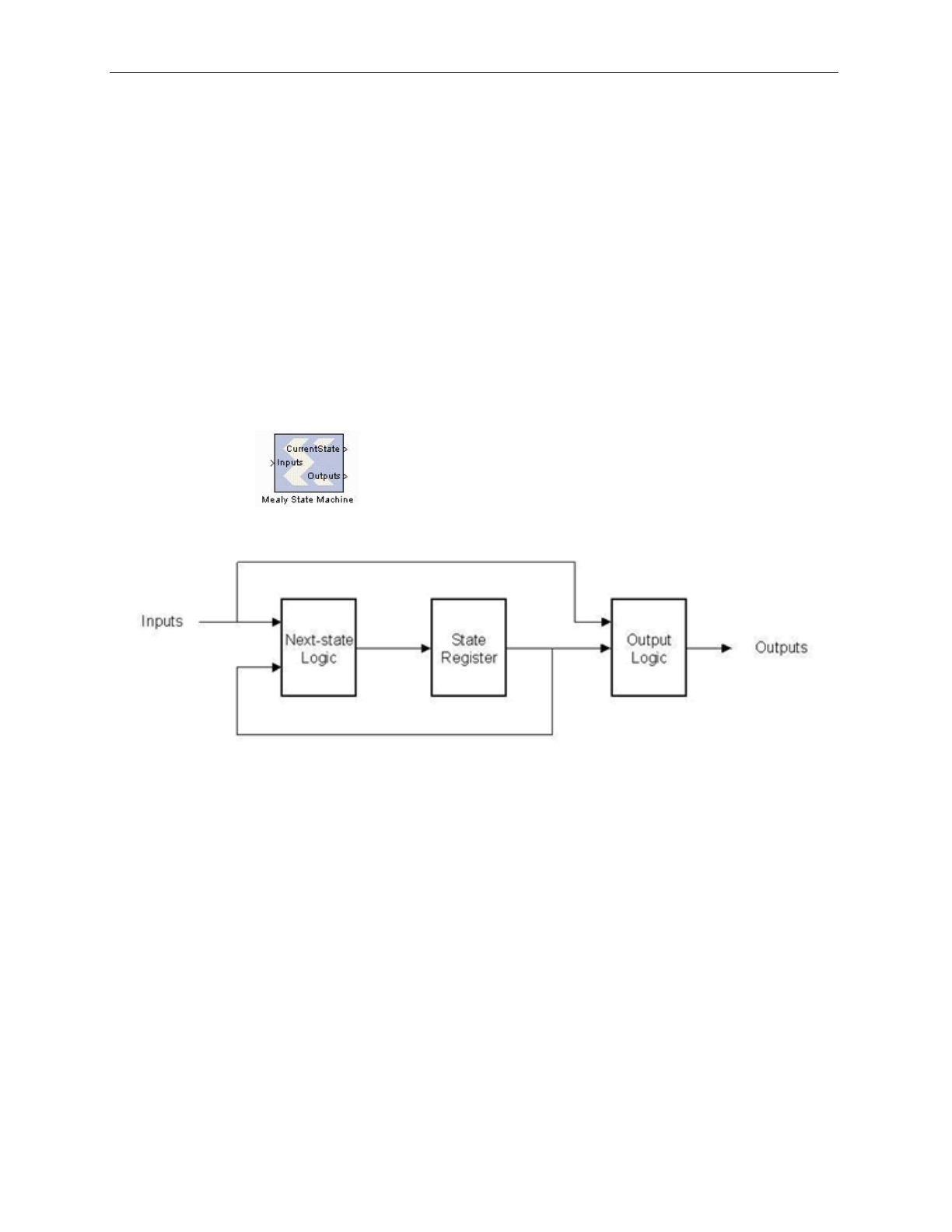

Mealy State Machine

The Xilinx Mealy State Machine block implements a state machine

whose output depends on both the current state and input.

A block diagram of this type of state machine is shown below:

Figure 3-76: Mealy State Machine block diagram

The block is configured by providing next state and output matrices. These matrices

are defined by the state machine’s next state/output table. For example, consider the

problem of designing a state machine to recognize the pattern ’1011’ within a serial