Math 89

Xilinx Blocks

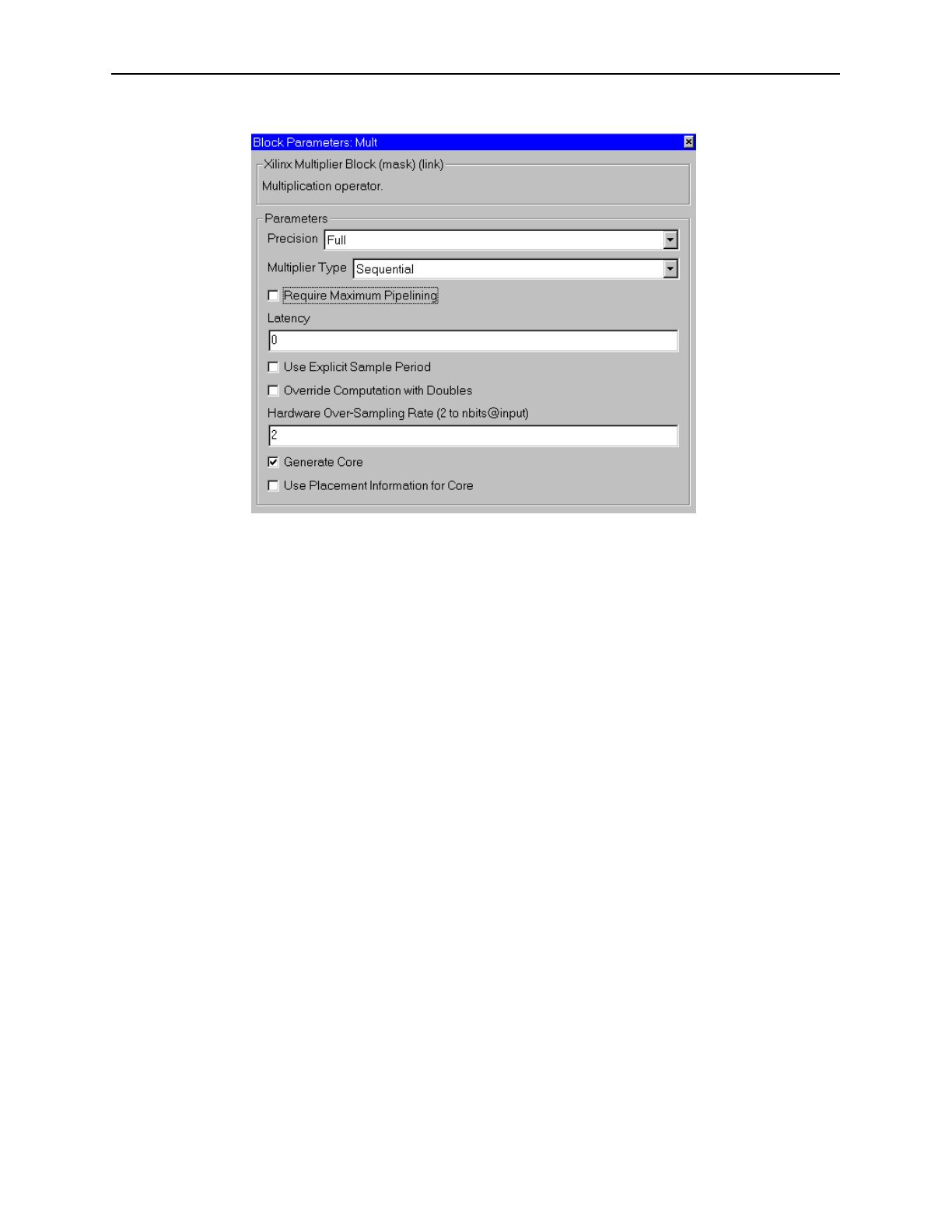

Figure 3-60: Mult block parameters dialog box - sequential type

Parameters specific to the Mult block are:

• Multiplier Type: directs the implementation to be either parallel or

sequential.

• Require Maximum Pipelining: directs the core to be pipelined to the fullest

extent possible.

• Use Dedicated High-Speed Multipliers: when checked, directs the core

to use embedded multipliers (available in Virtex-II only, and when the multiplier

type is parallel).

• Hardware Over-Sampling Rate: specifies the number of hardware cycles per

input sample; does not affect behavior in simulation, only the hardware

implementation.

• Use Placement Information for Core: allows specification of placement

layout shape that will be used when implementing the core in hardware

• Placement Style: specifies the layout shape in which the multiplier core will

be placed in hardware. The Rectangular option will generate a rectangular placed

core with loosely placed LUTs. Triangular packing will create a more compact

shape, with denser placement of LUTs.

Other parameters used by this block are explained in the Common Parameters section

of the previous chapter.

Xilinx LogiCORE

The Mult block always uses Xilinx LogiCORE: Multiply Generator V4.0.

The Core datasheet can be found on your local disk at:

%XILINX%\coregen\ip\xilinx\eip1\com\xilinx\ip\mult_gen_v4_0\do

c\mult_gen.pdf