56 Xilinx Development System

Xilinx System Generator v2.1 Reference Guide

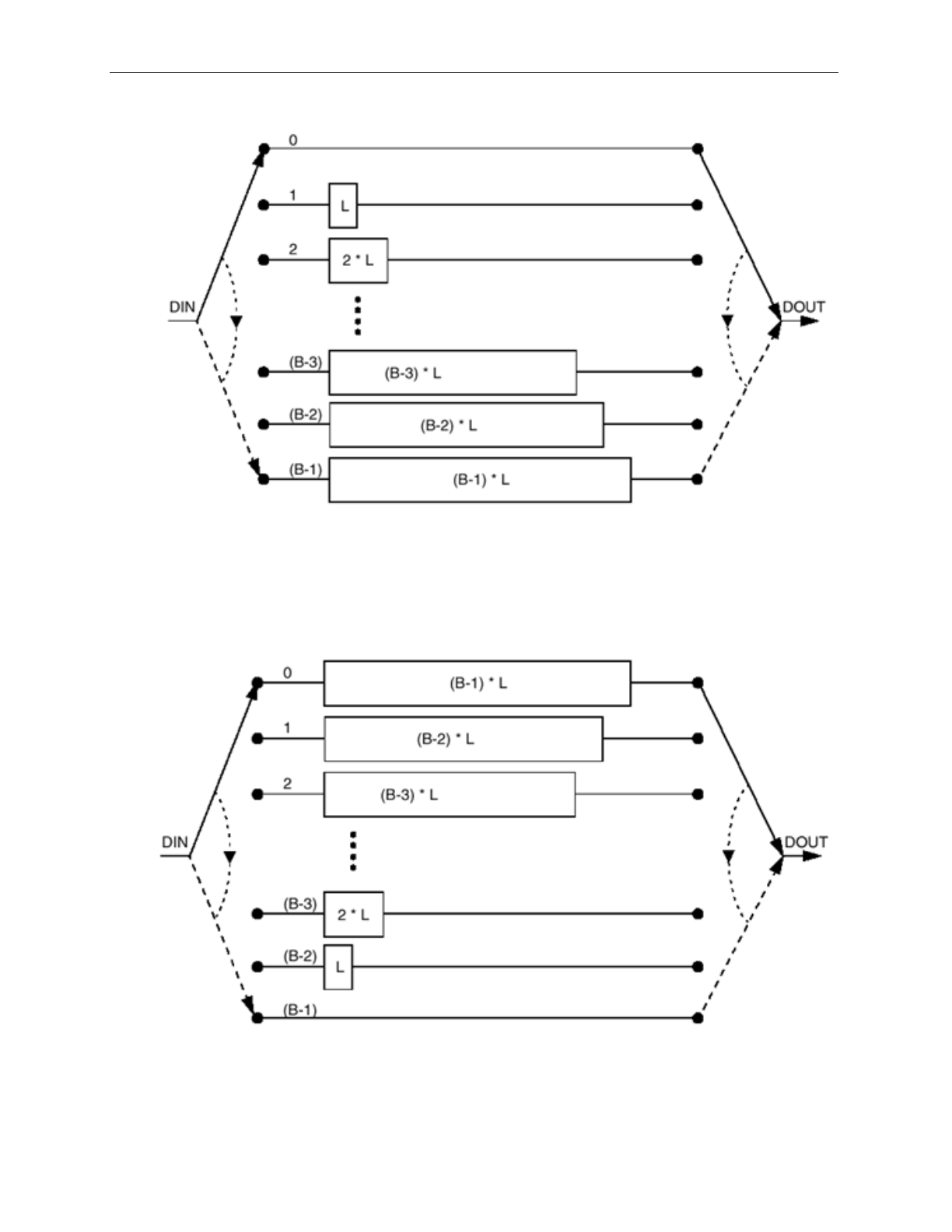

Figure 3-34: Forney convolutional interleaver with a constant difference

between consecutive branches

When the block is in deinterleaver mode, the input data sampled on the DIN port is

multiplexed into and out of B shift registers onto the DOUT port using two

(synchronized) commutator arms. Branch 0 will have a shift register of length (B-1)*L.

Branch (B-1) shall have a shift register length of zero.

Figure 3-35: Forney convolutional deinterleaver with a constant difference

between consecutive branches