726

FX3S/FX3G/FX3GC/FX3U/FX3UC Series

Programming Manual - Basic & Applied Instruction Edition

33 Extension File Register Control – FNC290 to FNC299

33.3 FNC292 – INITR / Initialize R and ER

33.3 FNC292 – INITR / Initialize R and ER

Outline

This instruction initializes extension registers (R) to “HFFFF” (<K-1>) in the RAM built into the PLC and extension file

registers in a memory cassette (flash memory) before data logging using the LOGR (FNC293) instruction.

In FX

3UC PLC before Ver. 1.30, use this instruction to initialize extension file registers (ER) before writing data to

them using SAVER (FNC291) instruction.

In FX

3UC PLC Ver. 1.30 or later and FX3U PLC, the INITER (FNC295) instruction is also provided to initialize only

extension file registers (ER) to "HFFFF" (<K-1>) in a memory cassette (flash memory) in units of sector.

→ For the SAVER (FNC291) instruction, refer to Section 33.2.

→ For the LOGR (FNC293) instruction, refer to Section 33.4.

→ For the INITER (FNC295) instruction, refer to Section 33.6.

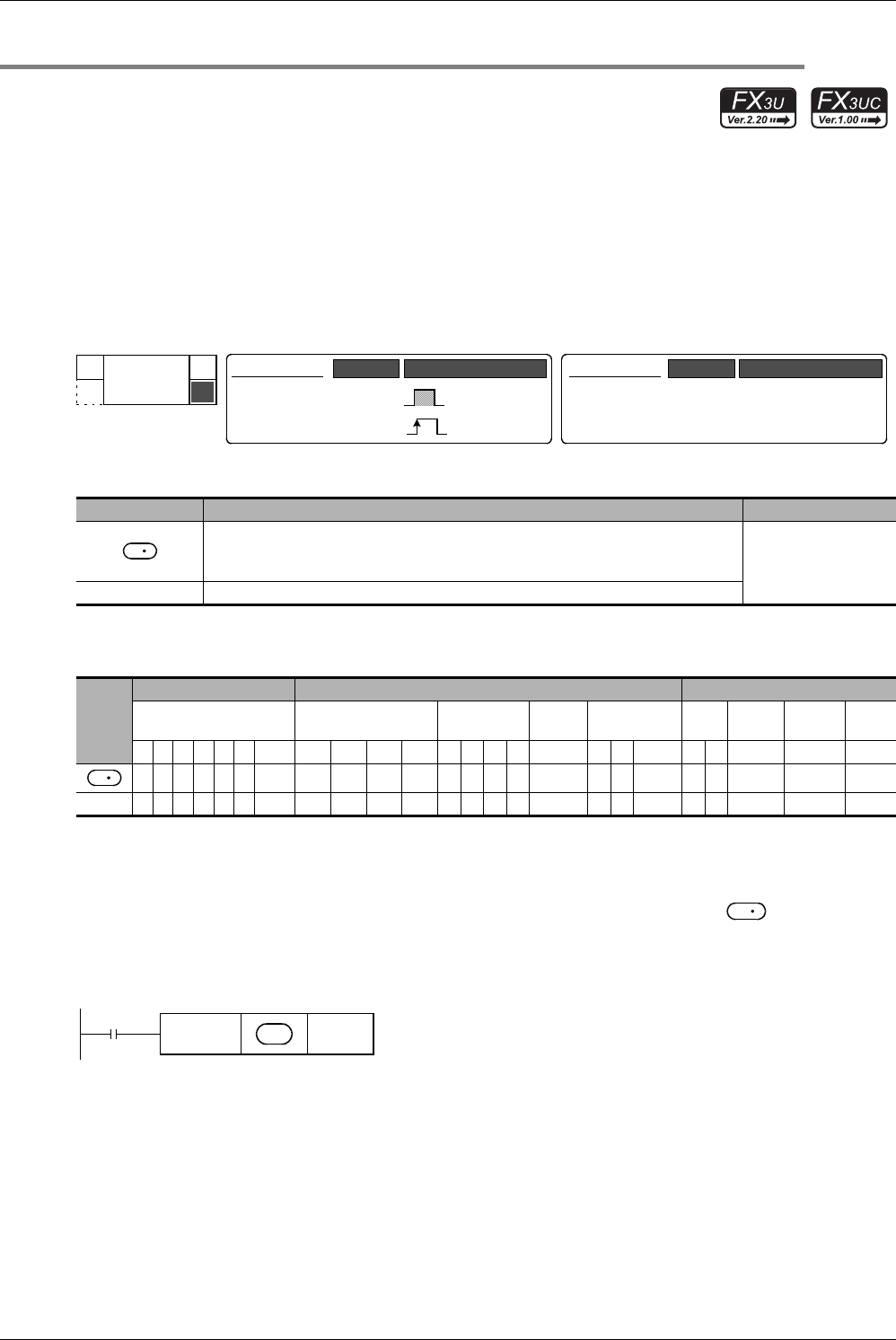

1. Instruction format

2. Set data

*1. When a memory cassette is not used, extension file registers (ER) are not initialized.

3. Applicable devices

Explanation of function and operation

1. 16-bit operation (INITR and INITRP)

“n” sectors of extension registers in the PLC’s built-in RAM starting from the one specified by and “n” sectors of

extension file registers in a memory cassette (flash memory) having the same device numbers are initialized to

“HFFFF” (<K-1>).

Initialization is executed in sector units.

Operand Type Description Data Type

Head device number of extension register and extension file register

*1

sector to be

initialized

It is possible to specify only the head device number in a sector of extension registers.

16-bit binary

n Number of sectors of extension registers and extension file registers to be initialized

Oper-

and

Type

Bit Devices Word Devices Others

System User Digit Specification System User

Special

Unit

Index

Con-

stant

Real

Number

Charac-

ter String

Pointer

XYMTCSD

.b KnX KnY KnM KnS T C D R

U\G

V Z Modify K H E "

"P

n

P

FNC 292

INITR

Mnemonic Operation Condition

16-bit Instruction

5 steps

INITR

Mnemonic Operation Condition

Continuous

Operation

32-bit Instruction

⎯

⎯

INITRP

Pulse (Single)

Operation

S

S

S

FNC292

INITRP

S

n

Command

input