709

FX3S/FX3G/FX3GC/FX3U/FX3UC Series

Programming Manual - Basic & Applied Instruction Edition

32 High-Speed Processing 2 – FNC280 to FNC289

32.1 FNC280 – HSCT / High-Speed Counter Compare With Data Table

31

FNC277-FNC279

Data

Transfer 3

32

FNC280-FNC289

High-Speed

Processing 2

33

FNC290-FNC299

Extension File

Register Control

34

FNC300-FNC305

FX

3U

-CF-ADP

35

SFC•STL

Programming

36

Interrupt

Function

37

Special Device

38

Error Code

A

Version Up

Information

B

Execution Times

32.1 FNC280 – HSCT / High-Speed Counter Compare With Data Table

Outline

This instruction compares the current value of a high-speed counter with a data table of comparison points, and then

sets or resets up to 16 output devices.

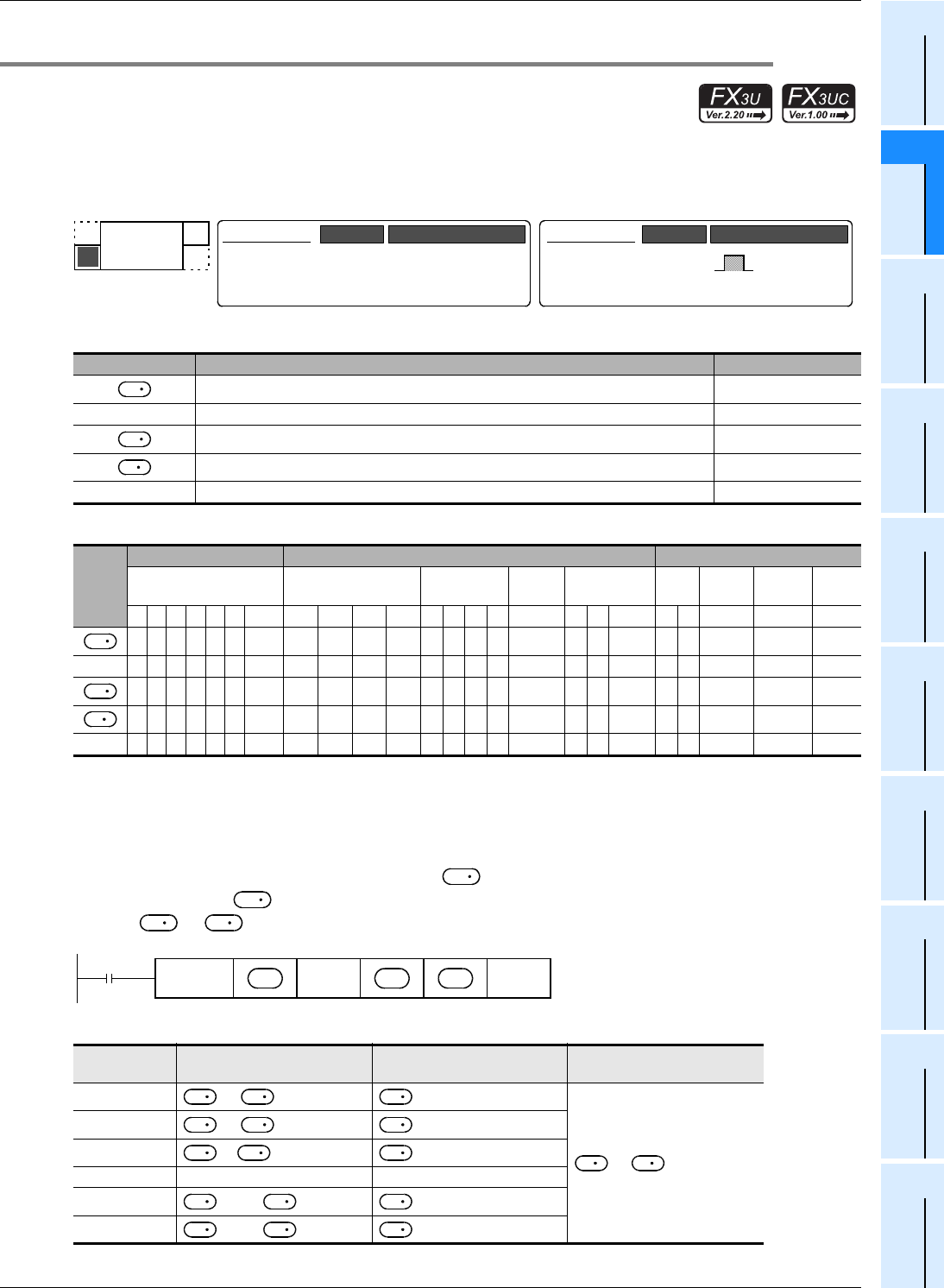

1. Instruction format

2. Set data

3. Applicable devices

Only a high-speed counter C235 to C255 can be specified in "S".

Explanation of function and operation

1. 32-bit operation (DHSCT)

The current value of a high-speed counter specified in is compared with the data table shown below which has

(3m) points stored in and later, and the operation output set value (ON or OFF) specified in the data table is

output to to +n-1.

Data table used for comparison

Operand Type Description Data Type

Head device number storing the data table 16- or 32-bit binary

m Number of comparison points in data table [1≤m≤128] 16-bit binary

High-speed counter number (C235 to C255) 32-bit binary

Head device number to which the operation status is output Bit

n Number of devices to which the operation status is output [1≤n≤16] 16-bit binary

Oper-

and

Type

Bit Devices Word Devices Others

System User Digit Specification System User

Special

Unit

Index

Con-

stant

Real

Number

Charac-

ter String

Pointer

XYMTCSD

.b KnX KnY KnM KnS T C D R

U\G

V Z Modify K H E "

"P

m

S

n

Comparison

point number

Comparison value

Operation output set value

(SET [1] or RESET [0])

Operation output destination

0

+1, +2

to +n-1

1

+4, +3 +5

2

+7 +6 +8

...

...

...

m-2

+3m-5, +3m-6 +3m-4

m-1

+3m-2, +3m-3 +3m-1

FNC 280

HSCT

D

Mnemonic Operation Condition

16-bit Instruction

21 steps

DHSCT

Mnemonic Operation Condition

Continuous

Operation

32-bit Instruction

⎯

⎯

⎯

S

1

S

2

D

S

1

S

2

D

S

2

S

1

D

D

FNC280

DHSCT

S

1

m D

nS

2

Command

input

S

1

S

1

S

1

D D

S

1

S

1

S

1

S

1

S

1

S

1

S

1

S

1

S

1

S

1

S

1

S

1