62 Language Dictionary

Description Of Common Commands

Table 7-1 shows the common commands and queries. These commands are listed alphabetically in the dictionary. If a

command has a corresponding query that simply returns the data or status specified by the command, then both command

and query are included under the explanation for the command. If a query does not have a corresponding command or is

functionally different from the command, then the query is listed separately. The description of each common command or

query specifies any status registers affected. In order to make use of this information, you must refer to "Chapter 4 - Status

Reporting", which explains how to read specific register bits and use the information that they return.

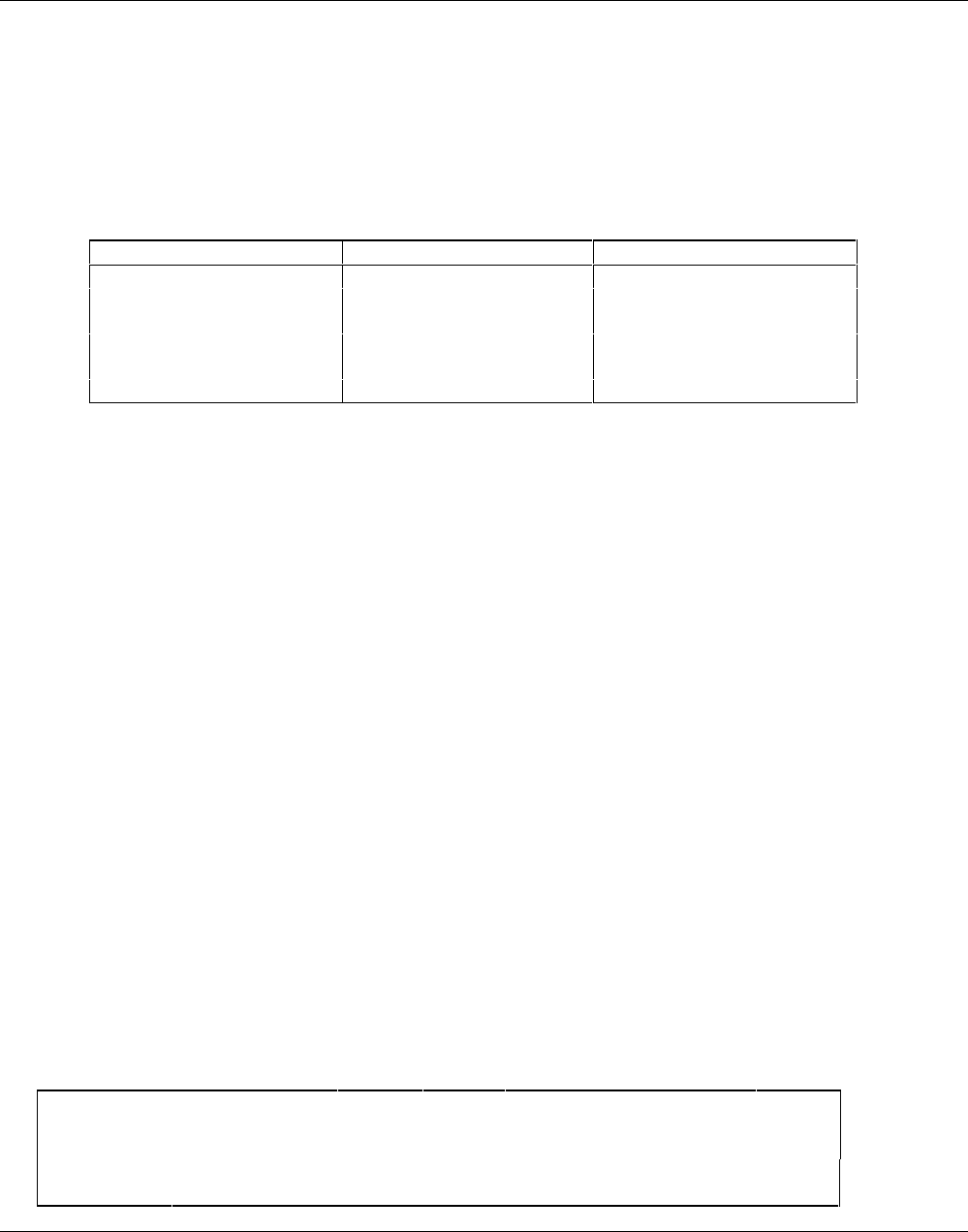

Table 7-1 Common Commands

Command Parameters Command Parameters Command Parameters

*CLS

(None)

*OPC?

(None)

*SRE <NRf>

*ESE <NRf> *PSC

<bool>

*SRE?

(None)

*ESE?

(None)

*PSC?

(None)

*STB?

(None)

*ESR?

(None)

*RCL <NRf> *TRG

(None)

*IDN?

(None)

*RST

(None)

*TST?

(None)

*OPC

(None)

*SAV <NRf> *WAI

(None)

*CLS

Meaning and Type

Clear Status Device Status

Description

This command causes the following actions (see "Chapter 4 - Status Reporting" for descriptions of all registers):

l Clears the Standard Event Status, Operation Status Event, Questionable Status Event, and Status Byte registers.

l Clears the Error Queue.

l If *CLS immediately follows a program message terminator (<NL>), then the output queue and the MAV bit are

also cleared.

Command Syntax *CLS

Parameters (None)

Query Syntax (None)

*ESE

Meaning and Type

Event Status Enable Device Status

Description

This command programs the Standard Event Status Enable register bits. The programming determines which events of the

Standard Event Status Event register (see *ESR?) are allowed to set the ESB (Event Summary Bit) of the Status Byte

register. A "1" in the bit position enables the corresponding event. All of the enabled events of the Standard Event Status

Event register are logically ORed to cause the Event Summary Bit (ESB) of the Status Byte register to be set. See

chapter 4 - "Status Reporting" for descriptions of all three registers.

Bit Configuration of Standard Event Status Enable Register

Bit Position

7 6 5 4 3 2 1 0

Bit Name

PON 0 CME EXE DDE QYE 0 OPC

Bit Weight

128 64 32 16 8 4 2 1

CME = Command error; DDE = Device-dependent error; EXE = Execution error;

OPC = Operation complete; PON Power-on; QYE = Query error.