MB91401

55

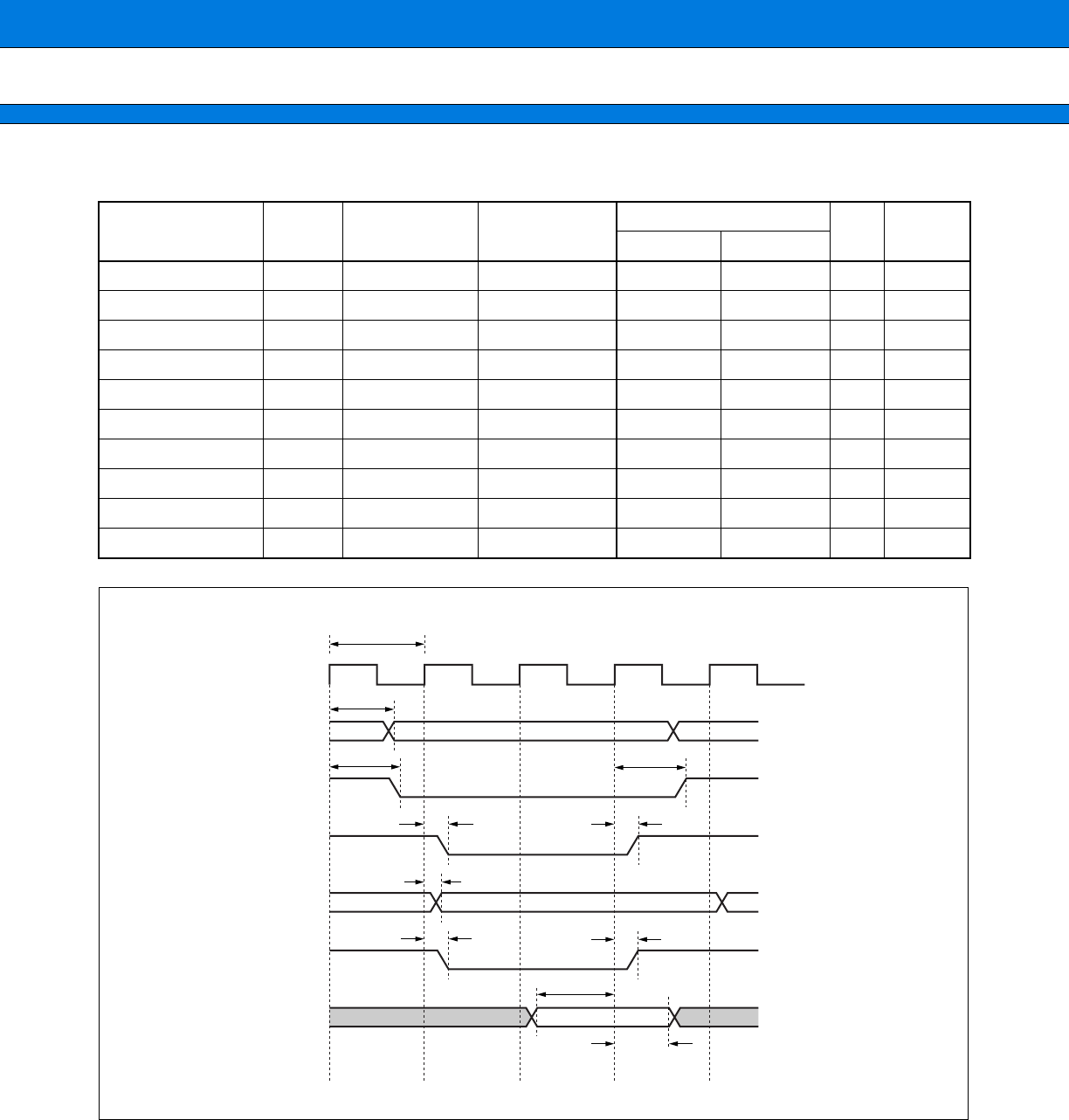

(3) Normal memory access

Note : tcycp is external memory clock cycle period.

Parameter Symbol Pin Typical timing

Value

Unit Remarks

Min Max

Address delay time tchav A23 to A0 MCLKO ↑ 0 tcycp / 2 + 7ns

CSX delay time tchcsl CSX2 to CSX0 MCLKO ↑ 0 tcycp / 2 + 7ns

CSX delay time tchcsh CSX2 to CSX0 MCLKO ↑ 0 tcycp / 2 + 7ns

WRX delay time tchwrl WRX3 to WRX0 MCLKO ↑ − 19ns

WRX delay time tchwrh WRX3 to WRX0 MCLKO ↑ − 19ns

Data delay time tchdv D31 to D0 MCLKO ↑ 0 tcycp / 2 + 7ns

RDX delay time tchrdl RDX MCLKO ↑ − 19ns

RDX delay time tchrdh RDX MCLKO ↑ − 19ns

Data setup tdsrh D31 to D0 MCLKO ↑ 19 ns

Data hold trhdx D31 to D0 MCLKO ↑ − 1 ns

tcycp

tchav

tchcsl

tchwrl

tchdv

tchrdl

tdsrh

tchrdh

tchwrh

tchcsh

trhdx

MCLKO

A23 to A0

CSX2 to CSX0

WRX3 to WRX0

D31 to D0

RDX

D31 to D0

Prelminary

2004.11.12