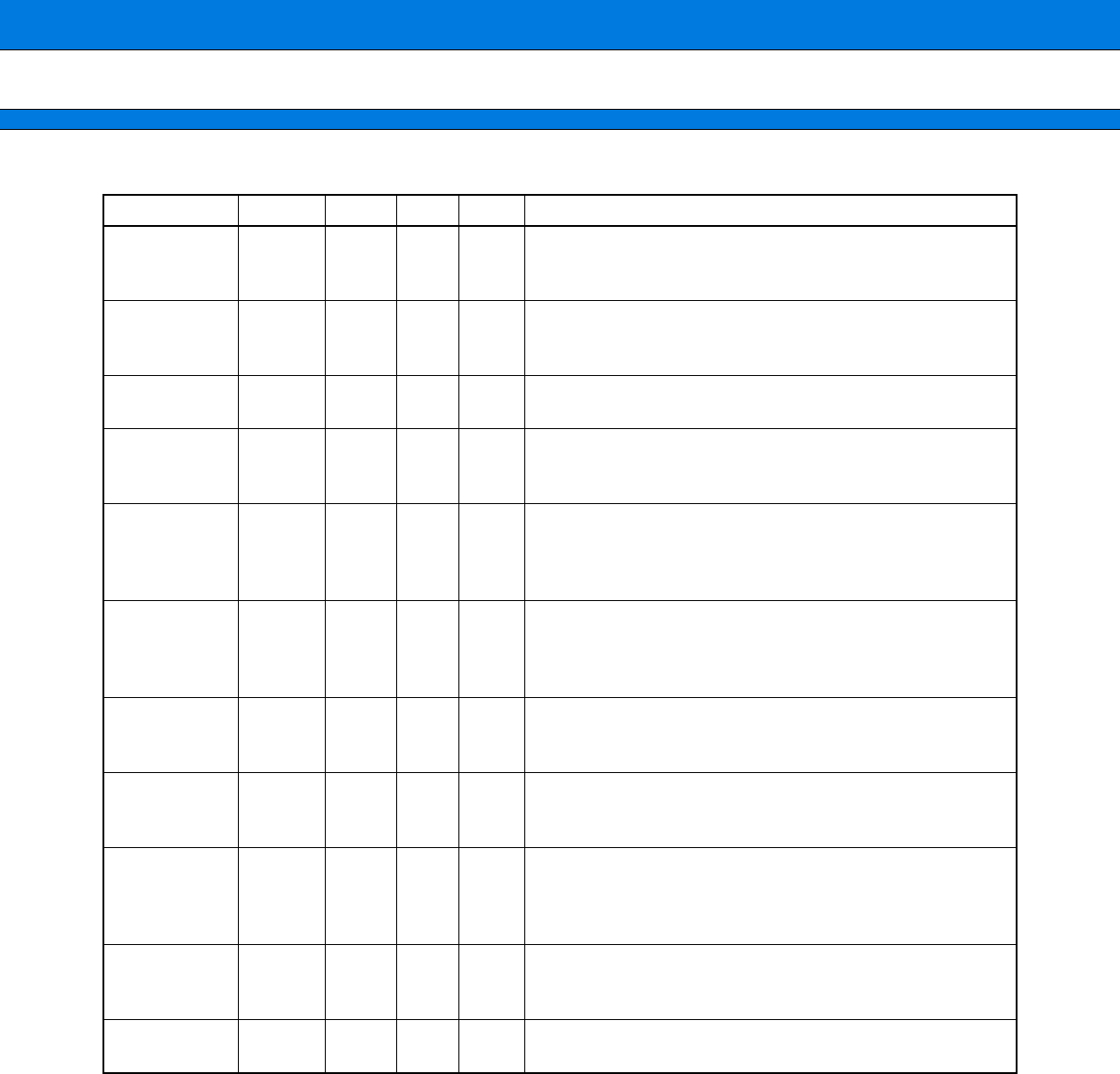

MB91401

11

ETHERNET MAC CONTROLLER (17 pin)

Pin name Pin no.

Polarity

I/O

Circuit

Function/application

RXCLK 48 IN D

Clock input for reception pin

MII sync signal during reception. The frequency is 2.5 MHz

at 10 Mbps and 25 MHz at 100 Mbps.

RXER 113

Posi-

tive

IN D

Receive error input pin

It is recognized that there is an error in the reception packet

when “1” is input from the PHY device at receiving.

RXDV 172

Posi-

tive

IN D

Receive data valid input pin

It is recognized that receive data is effective.

RXCRS 115

Posi-

tive

IN D

Career sense input pin

The state that the reception or the transmission is done is

recognized.

RXD3

RXD2

RXD1

RXD0

114

47

112

45

IN D

Receive data input pins

4-bit data input from PHY device.

COL 173

Posi-

tive

IN D

Collision detection input pin

When TXEN signal is active and “1”, the collision is

recognized. The collision is not recognized without these

conditions.

TXCLK 46 IN D

Clock input for transfer pin

It becomes synchronous of MII when transmitting. The

frequency is 2.5 MHz at 10 Mbps and 25 MHz at 100 Mbps.

TXEN 43

Posi-

tive

OUT F

Transfer enable output pin

It is shown that effective data is on the TXD bus. It is output

synchronizing with TXCLK.

TXD3

TXD2

TXD1

TXD0

171

170

111

44

OUT F

Transfer data output pins

4-bit data bus sent to the PHY device. It is output

synchronizing with TXCLK.

MDCLK 222 OUT F

SMI clock output pin

SMI IF clock pin

Connect to SMI clock input pin of PHY device.

MDIO 224 I/O B

SMI data input/output pin

Connect to SMI data of PHY device.

Prelminary

2004.11.12