75 Appendix C

C.16 Clear FIFO Interrupt Request — BASE+14H

Write any value to this I/O port to clear the FIFO's interrupt request.

C.17 A/D Data and Channel from FIFO - BASE + 17/18H

The PCL-818HD/HG stores data from A/D conversions in a 1 K word

First-In First-Out (FIFO) data buffer. Registers at BASE+17H and

BASE+18H store the channel number and data. The register at

BASE+19H clears the FIFO buffer and sets its empty flag (EF).

AD11 ~ AD0 Analog to digital data

AD0 The least significant bit (LSB) of the A/D data

AD11 The most significant bit (MSB)

C3 ~ C0 A/D channel number from which the data is derived

C0 The least significant bit (LSB) of the channels

C3 The most significant bit (MSB)

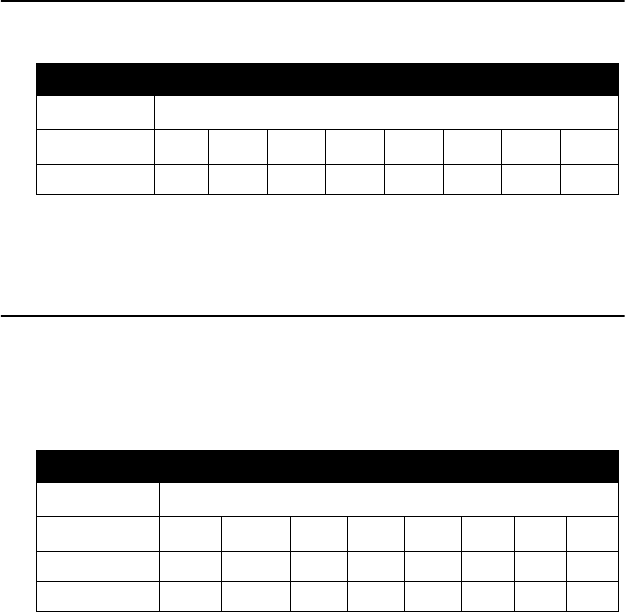

Table C.17: Register for Clear FIFO Interrupt Request

Write Clear FIFO Interrupt Request

Bit # 76543210

BASE + 14H X X X X XXXX

Table C.18: Register for A/D Data and Channel from FIFO

Read A/D data and channels from FIFO

Bit # 7 6 543210

BASE + 17H AD3 AD2 AD1 AD0 C3 C2 C1 C0

BASE + 18H AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4