PCI-1718 Series User Manual 28

3.3 Signal Connections

Pin Assignment

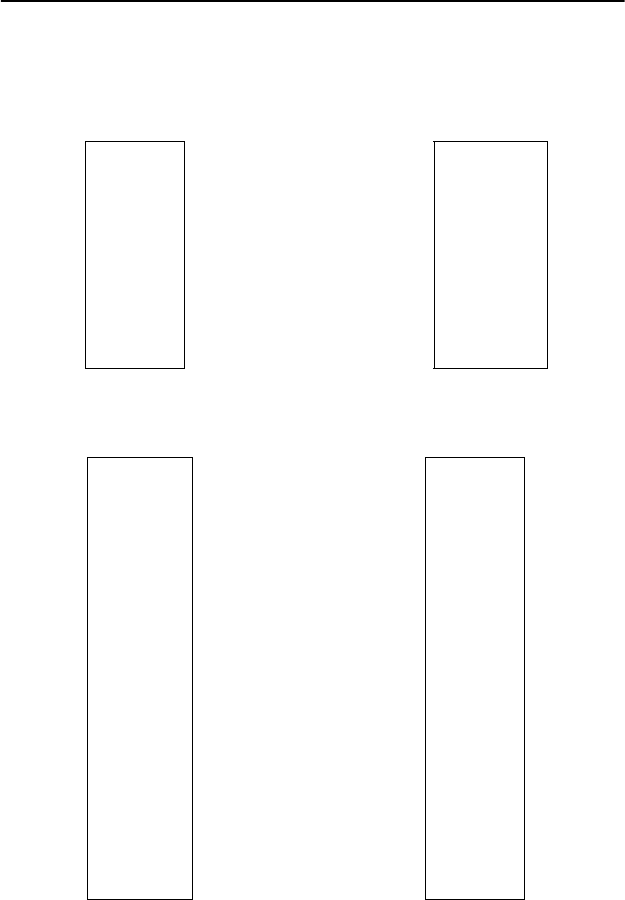

Figure 3-2 shows the pin assignments for the 37-pin I/O connector on the

PCI-1718HDU/HGU.

Figure 3.2: I/O Connector Pin Assignments for the PCI-1718 Series

Note: S0/S1 is NC, and S2/S3 is AGND for PCI-1718HGU

CN1 CN2

D/O 0 1 2 D/O 1 D/I 0 1 2 D/I 1

D/O 2 3 4 D/O 3 D/I 2 3 4 D/I 3

D/O 4 5 6 D/O 5 D/I 4 5 6 D/I 5

D/O 6 7 8 D/O 7 D/I 6 7 8 D/I 7

D/O 8 9 10 D/O 9 D/I 8 9 10 D/I 9

D/O 10 11 12 D/O 11 D/I 10 11 12 D/I 11

D/O 12 13 14 D/O 13 D/I 12 13 14 D/I 13

D/O 14 15 16 D/O 15 D/I 14 15 16 D/I 15

D.GND 17 18 D.GND D.GND 17 18 D.GND

+5 V 19 20 +12 V +5 V 19 20 +12 V

CN3 (Single ended) CN3 (Differential)

A/D S0 1 20 A/D S8 A/D H0 1 20 A/D L0

A/D S1 2 21 A/D S9 A/D H1 2 21 A/D L1

A/D S2 3 22 A/D S10 A/D H2 3 22 A/D L2

A/D S3 4 23 A/D S11 A/D H3 4 23 A/D L3

A/D S4 5 24 A/D S12 A/D H4 5 24 A/D L4

A/D S5 6 25 A/D S13 A/D H5 6 25 A/D L5

A/D S6 7 26 A/D S14 A/D H6 7 26 A/D L6

A/D S7 8 27 A/D S15 A/D H7 8 27 A/D L7

A.GND 9 28 A.GND A.GND 9 28 A.GND

A.GND 10 29 A.GND A.GND 10 29 A.GND

VREF 11 30 DA0.OUT VREF 11 30 DA0.OUT

S0* 12 31 DA0.VREF S0* 12 31 DA0.VREF

+12 V 13 32 S1* +12 V 13 32 S1*

S2* 14 33 S3* S2* 14 33 S3*

D.GND 15 34 D.GND D.GND 15 34 D.GND

NC 16 35 EXT.TRIG NC 16 35 EXT.TRIG

Counter 17 36 Counter 0 Counter 0 17 36 Counter 0

Counter 18 37 PACER Counter 0 18 37 PACER

+5 V 19 +5 V 19

..