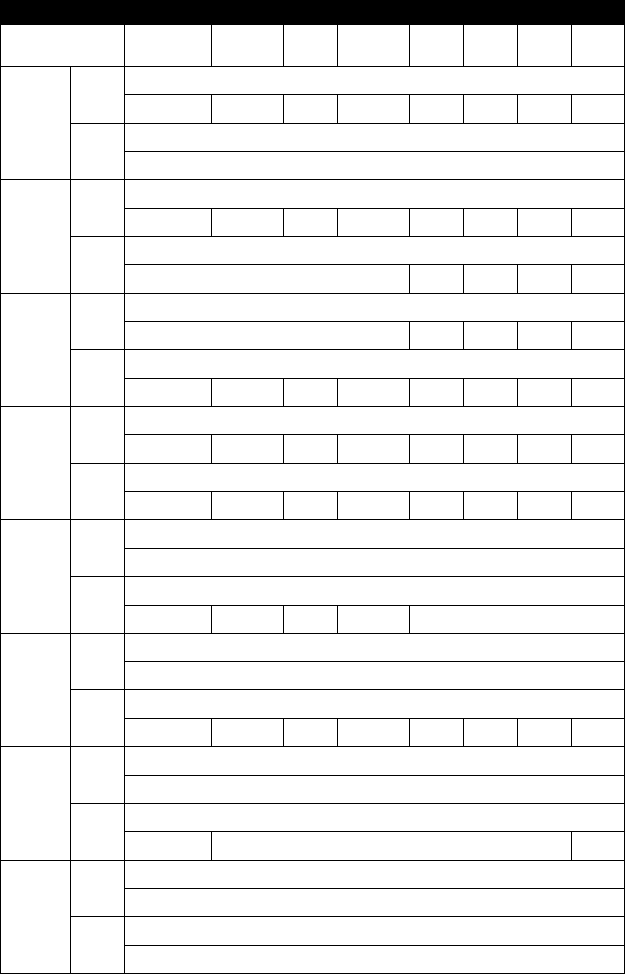

61 Appendix C

Table C.1: PCI-1718HDU/HGU Register Format (Part 1)

Base Addr.

+HEX

7 6 54 3210

00H

R

A/D low byte data and channels

AD3 AD2 AD1 AD0 C3 C2 C1 C0

W

Software A/D trigger

01H

R

A/D high byte data and channels

AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4

W

A/D range control

G3 G2 G1 G0

02H

R

MUX scan channel status

CC3 CC2 CC1 CC0

W

MUX scan channel control

CH3 CH2 CH1 CH0 CL3 CL2 CL1 CL0

03H

R

Digital Input (low byte)

DI7 DI6 DI5 DI4 DI3 DI2 DI1 DI0

W

Digital Output (low byte)

DO7 DO6 DO5 DO4 DO3 DO2 DO1 DO0

04H

R

N/A

W

D/A output data

DA3 DA2 DA1 DA0

05H

R

N/A

W

D/A output data

DA11 DA10 DA9 DA8 DA7 DA6 DA5 DA4

06H

R

N/A

W

AD resolution & FIFO interrupt control

AD12_16 FINT

07H

R

N/A

W

N/A