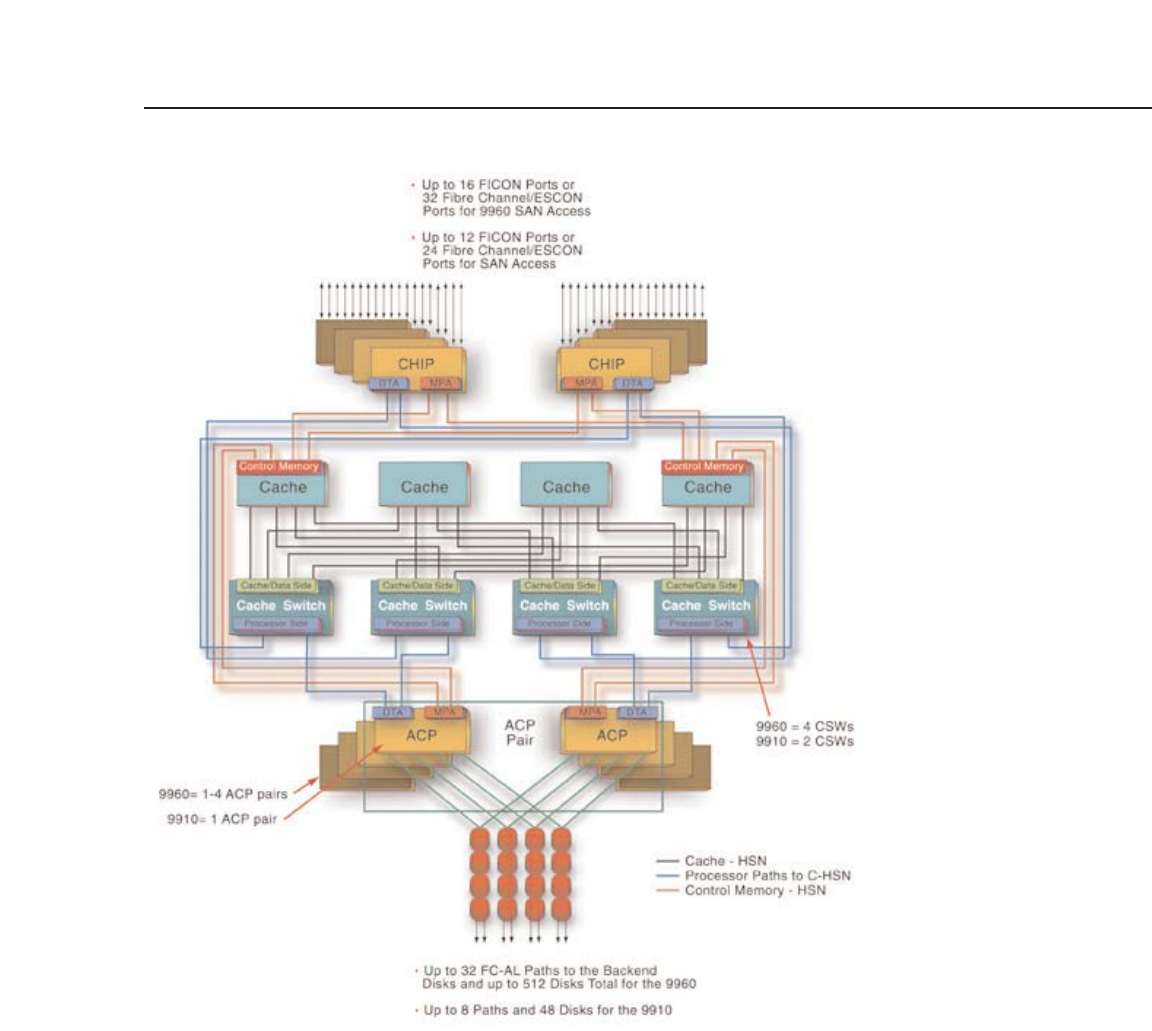

At the heart of the Lightning 9900

™

Series’ enormous capacity for throughput lies

the Hi-Star

™

architecture. This network of interconnecting high-speed links to system

components provides an unequaled internal aggregate bandwidth of 6.4GB/sec

(gigabytes/sec) in the 9960. This bandwidth is divided equally into 3.2GB/sec for data

transfer and 3.2GB/sec for separate internal control information transfer.

The main components that make up the Lightning 9900

™

Series are the Array Control

Processor modules (ACPs), Host Adapter modules, called Client Host Interface Processors

(CHIPs). These elements enable the unsurpassed bandwidth of the Hi-Star

™

network by

bringing their own network paths (and bandwidth) to the Cache Hierarchical Star Network

(C-HSN) and the Control Memory Hierarchical Star Network (CM-HSN). This means

that the full 6.4GB/sec internal bandwidth is available with a fully configured 9960 with all

four ACP pairs (eight modules total) and all four CHIP pairs (eight modules total). This is

a truly high-performance and cost-effective configuration. With any Lightning 9900

™

Series

configuration, growing or scaling can be easily completed by adding more CHIP pairs for

connectivity or ACP pairs for more capacity or performance. The internal bandwidth

increases every time components are added. The bandwidths stated are the rated

bandwidths for the paths; the effective rates will vary based on application workload and

bandwidth consumption.

Figure 2 – The Hitachi

Lightning 9960

™

Series’

Hi-Star

™

internal

switched-fabric

architecture.

3

Introduction