1-14

MDrive 34Plus

Microstepping Hardware - Revision R071108

Relevant to Firmware Version 3.0.02

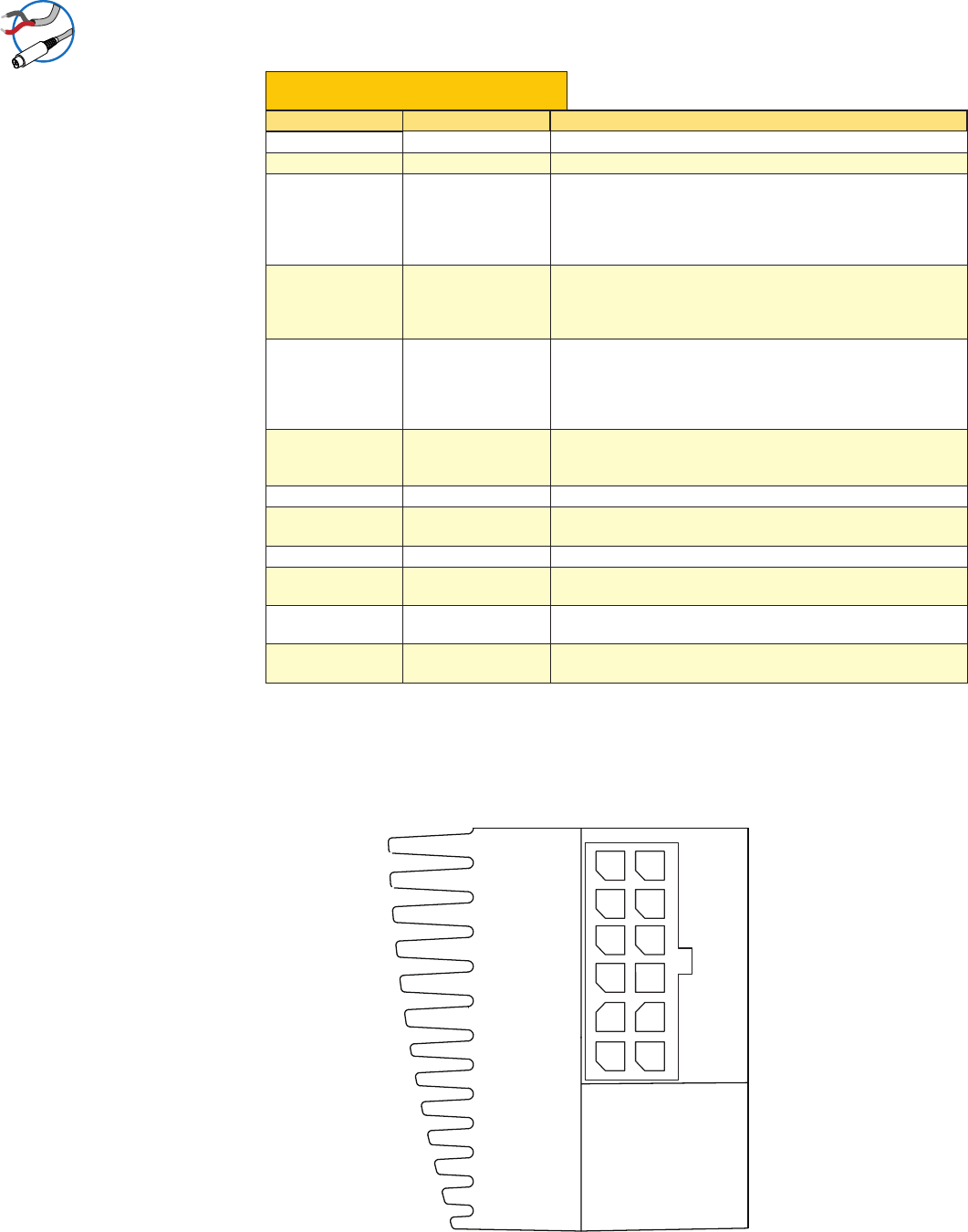

Pin Assignment And Description - Pluggable Interface Version

P1 Connector - I/O and SPI Communications, 12-Pin Locking Wire Crimp

Pin Assignment - P1 Power, I/O and SPI

Connections

Pin # Function Description

Pin 1 N/C No Connect.

Pin 2 N/C No Connect.

Pin 3 Opto Reference

The Signal applied to the Optocoupler Reference will

determine the sinking/ or sourcing configuration of the inputs.

To set the inputs for sinking operation, a +5 to +24 VDC

supply is connected. If sourcing, the Reference is connected

to Ground

Pin 4

Step Clock/Channel

A/ Clock Up

Step Clock input. The step clock input will receive the clock

pulses which will step the motor 1 step for each pulse. It

may also receive quadrature and clock up type inputs if so

configured.

Pin 5 Enable

Enable/Disable Input will enable or disable the driver output

to the motor. In the disconnected state the driver outputs are

enabled in either sinking or sourcing configuration. Enable can

be configured as either active high or active when low in the

parameters.

Pin 6

Direction/Channel

B/ Clock Down

Direction input. The axis direction will be with respect to the

state of the Direction Override Parameter. It may also receive

quadrature and clock up type inputs if so configured.

Pin 7 +5 VDC Output Supply voltage for the MD-CC300-000 Cable ONLY!

Pin 8 SPI Clock

The Clock is driven by the SPI Master. The clock cycles once

for each data bit.

Pin 9 GND Communications Ground.

Pin 10 MOSI

Master-Out/Slave-In. Carries output data from the SPI Master

to the MDM.

Pin 11 CS

SPI Chip Select. This signal is used to turn communications

on multiple MDM units on or off.

Pin 12 MISO

Master-In/Slave-Out. Carries output data from the MDM back

to the SPI Master.

Table 1.2.10: P1 Connector – I/O and SPI Communications

NEED A CABLE?

The following

cables and

converters are

available to

interface with P1:

12-Pin Locking Wire Crimp

PD12-1434-FL3

11

9

7

5

3

1

12

10

8

6

4

2

Recommended Cable:

PD12-1434-FL3

Figure 1.2.7: P2 Connector - I/O and SPI Communications